R6500 NMOS PRODUCTS R6500 NMOS PRODUCTS

NMOS MEMORY PRODUCTS NMOS MEMORY PRODUCTS

PPS PMOS PRODUCTS

PPS PM0S PR00UCTS

**Microelectronic Devices**

Data Catalog

MICROMODEM MODULES MICROMODEM MODULES

BUBBLE MEMORY PRODUCTS BUBBLE MEMORY PRODUCTS

FILTER PRODUCTS

FILTER

TELECOM DEVICES

TELECOM

#### TABLE OF CONTENTS

#### **R6500 NMOS PRODUCTS**

#### **R6500 Family Brochure**

#### R6500 CPUs & R6500/1

R6500 CPUs

R6500B Series (3 MHz) CPUs

R6500/1 One Chip Microcomputer

R6500/1E Emulator Device

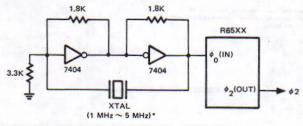

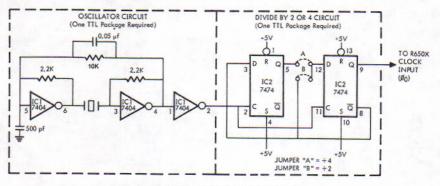

Clock Input (Application Note)

#### R6500 I/O Devices

R6520 Peripheral Interface Adapter (PIA)

R6522 Versatile Interface Adapter (VIA)

R6541 Programmable Keyboard/Display Controller (PKDC)

R6545 CRT Controller (CRTC)

R6551 Asynchonous Communication Interface Adapter (ACIA)

#### R6500 Memory-I/O Combination Devices

R6530 ROM-RAM-I/O-Timer (RRIOT) R6531 ROM-RAM-I/O-Counter (RRIOC) R6532 RAM-I/O-Timer (RIOT) R6534 ROM-I/O-Counter (RIOC)

#### **R6500 Support Products**

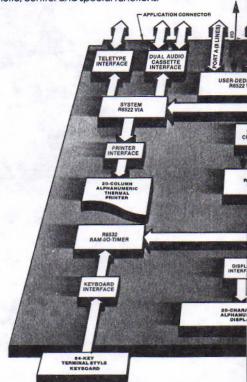

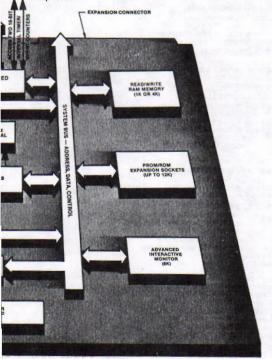

AIM 65 Microcomputer

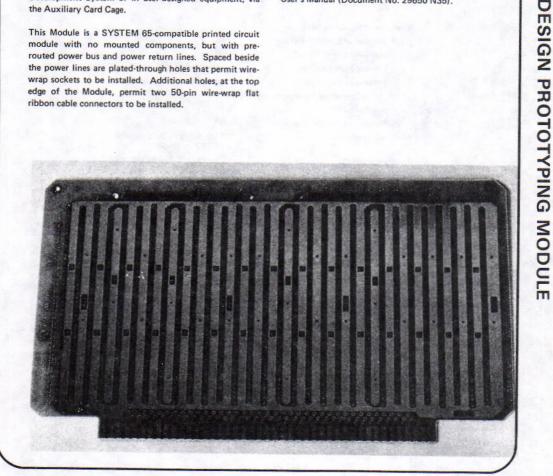

SYSTEM 65 Microcomputer Development System M65-001, M65-002 USER 65 Option M65-031, M65-032 16K Static RAM Module M65-040 PROM Programmer Module M65-045 PROM/ROM Module M65-060 Extender Card M65-070 Design Prototyping Module

PL/65 Compiler

#### NMOS MEMORY PRODUCTS

**RAM Memory Devices**

R2114 1024 x 4 Static RAM

#### **ROM Memory Devices**

R2316 2048 x 8 Static ROM R2332 4096 x 8 Static ROM

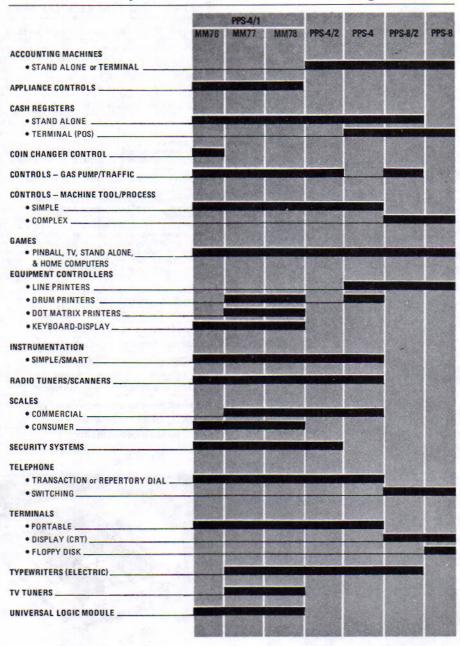

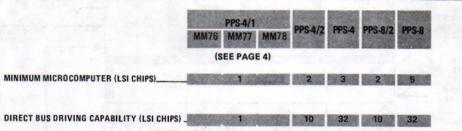

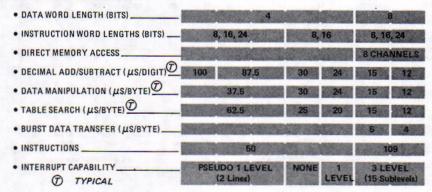

#### PPS PMOS PRODUCTS

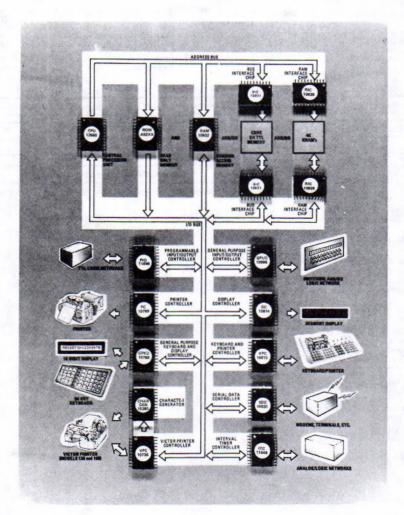

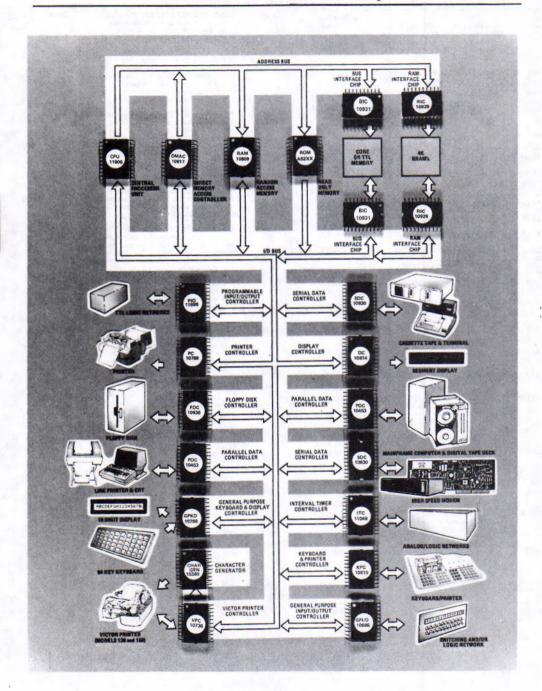

**PPS Family Brochure**

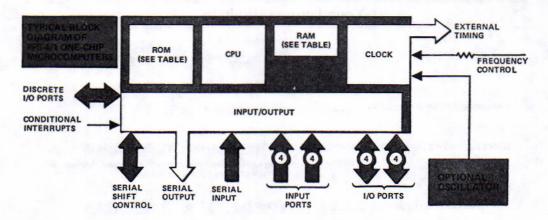

#### PPS-4/1 One-Chip Microcomputers

MM76 and MM76E MM75 MM76C MM76L and MM76EL MM77 and MM78 MM77L and MM78L Serial Communications Protocol for Multiple PPS-4/1 Systems (Application Note) A THE RESERVE

BYOM OWNERS BUSINESS

A William Control of

CALL THE STATE OF THE STATE OF

A CONTRACTOR OF STREET

and a strongly of the control of the configuration of the configuration

THE SECTION AND SECTION ASSESSMENT AND ADDRESS.

the community of the 420.00

STORY FOREST STORY

100 to 10

The stoppe of the stoppe of

The second second

the second and the second

90.00

CONTRACTOR STREET

Sand the region of

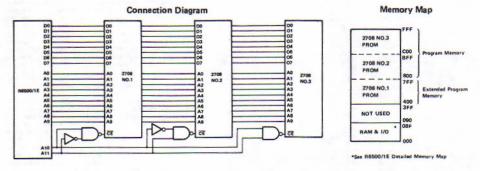

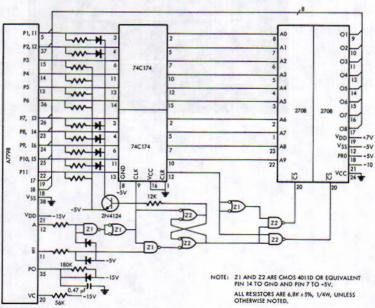

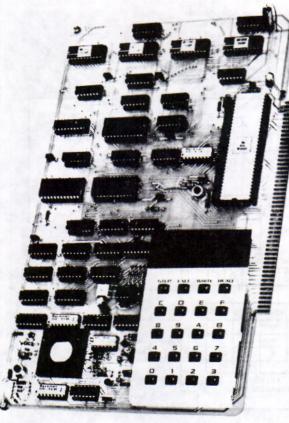

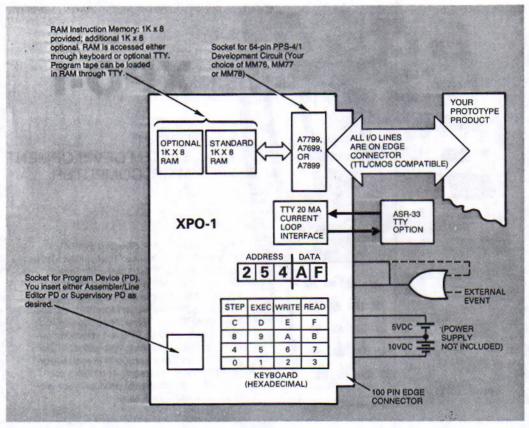

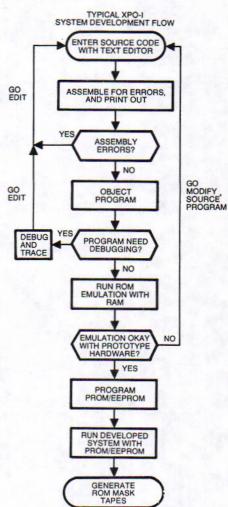

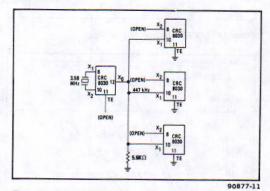

PPS-4/1 Prototyping with 2708 PROMs (Application Note) XPO-1 Sytem Development Microcomputer

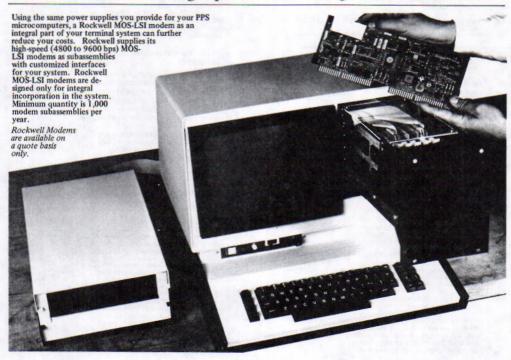

#### MICROMODEM MODULES

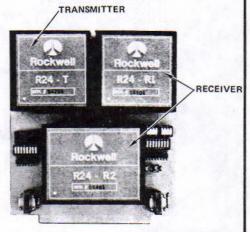

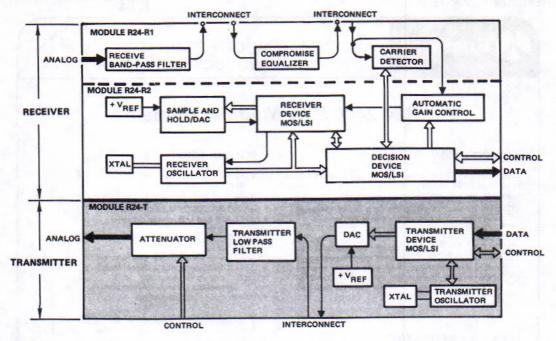

R24 2400 BPS Modular Modem

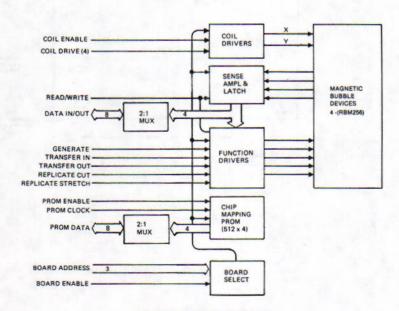

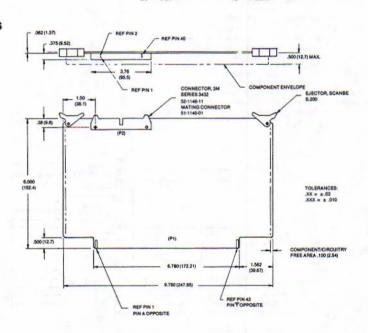

#### **BUBBLE MEMORY PRODUCTS**

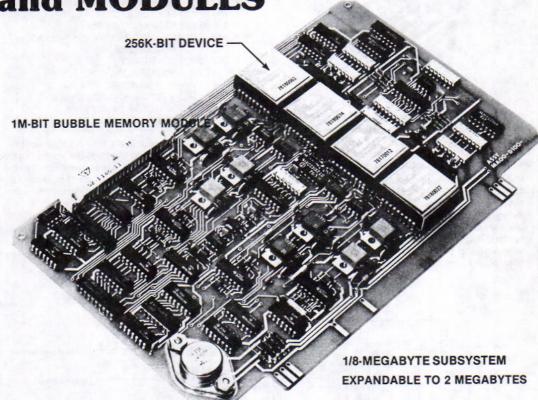

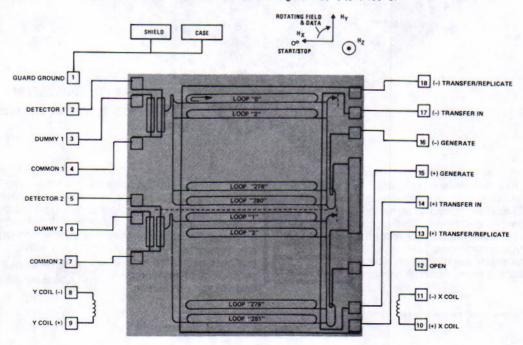

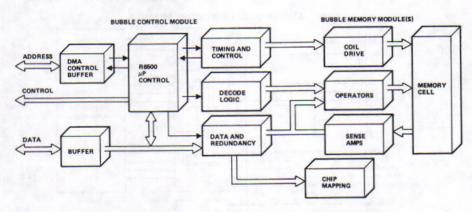

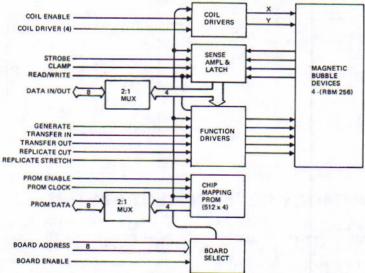

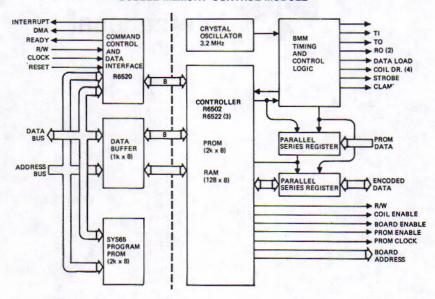

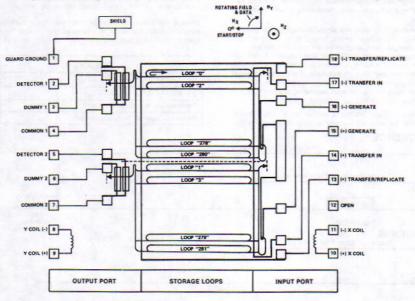

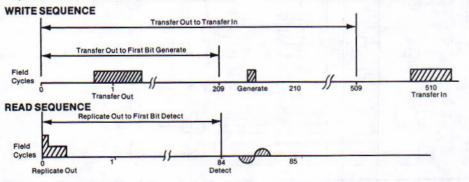

Bubble Memory Brochure RBM256 256K-Bit Bubble Memory Device RLM658 1-Megabit Linear Bubble Memory Module

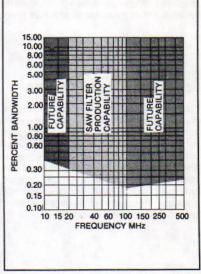

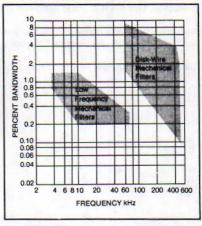

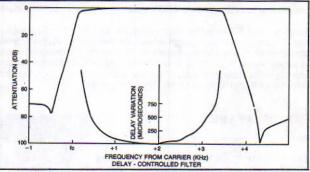

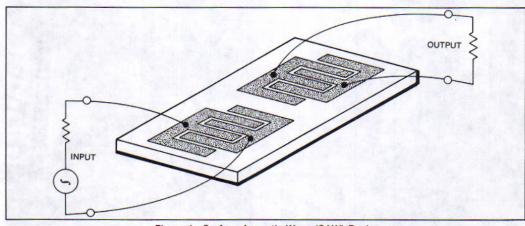

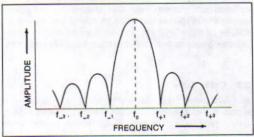

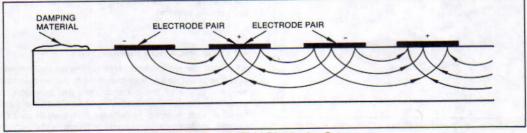

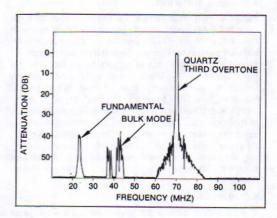

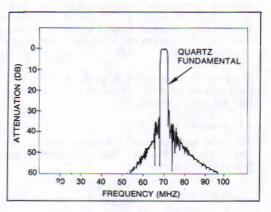

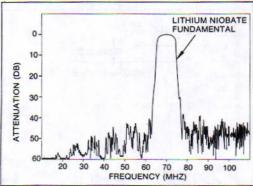

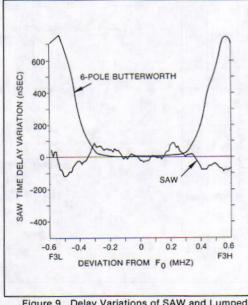

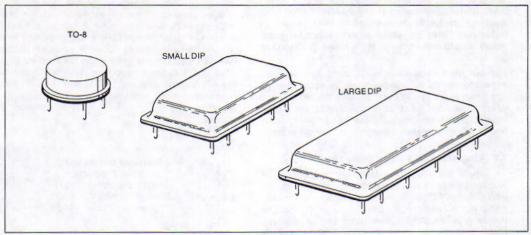

#### **ROCKWELL-COLLINS FILTER PRODUCTS**

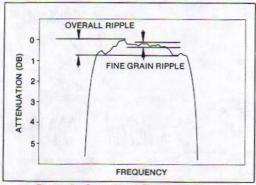

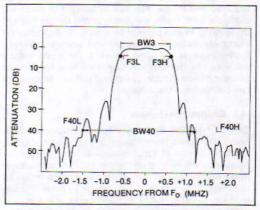

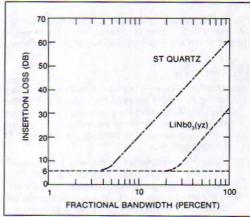

Filter Products Flyer Low Frequency Mechanical Filters Brochure Surface Wave Acoustic Devices Brochure

#### **TELECOM DEVICES**

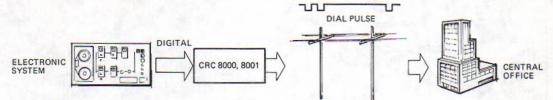

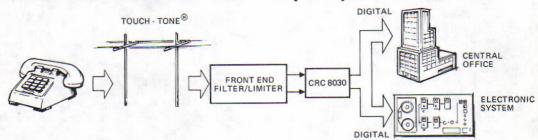

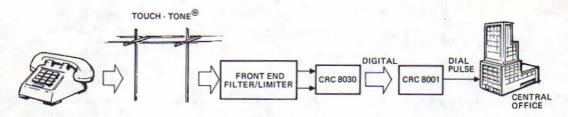

Telecommunication Products Flyer

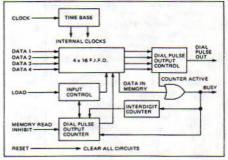

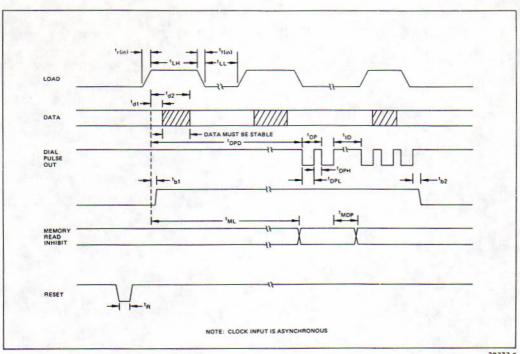

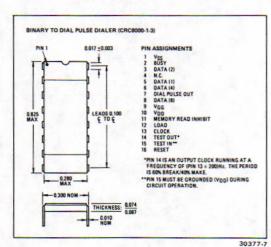

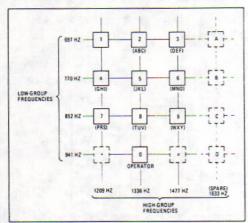

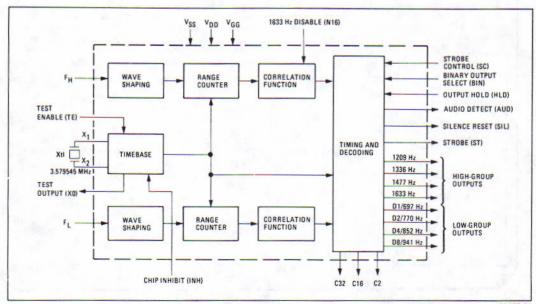

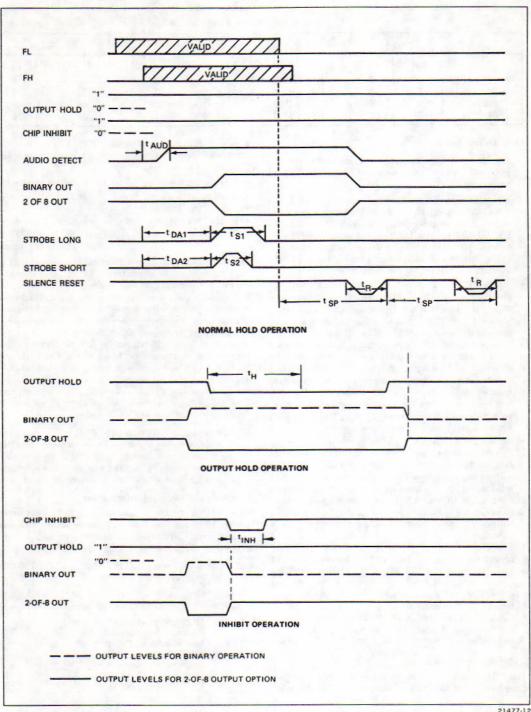

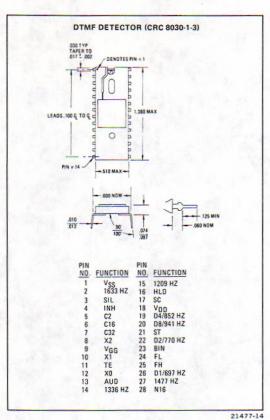

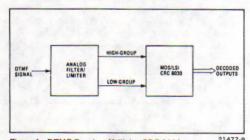

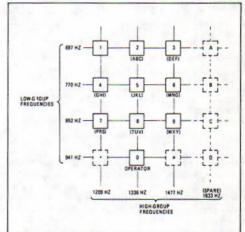

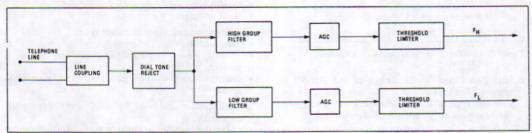

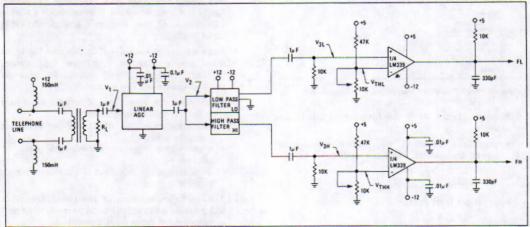

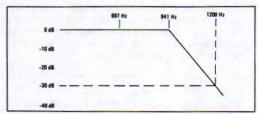

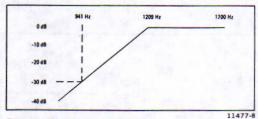

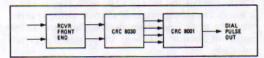

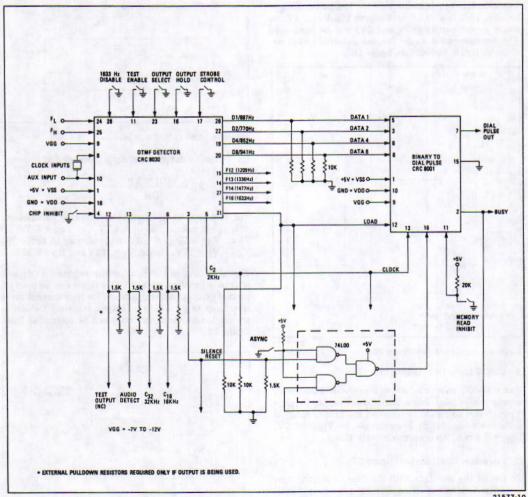

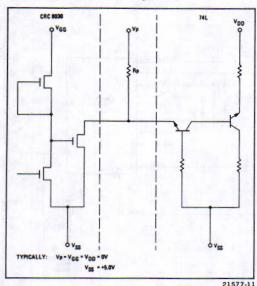

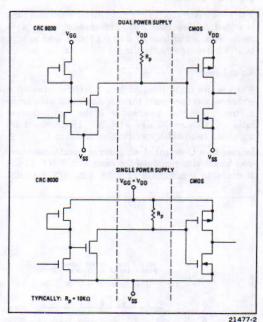

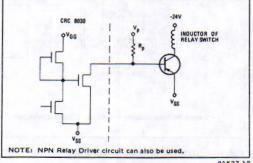

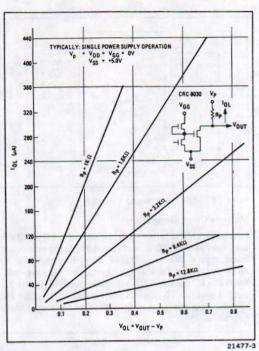

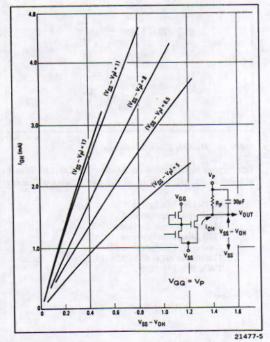

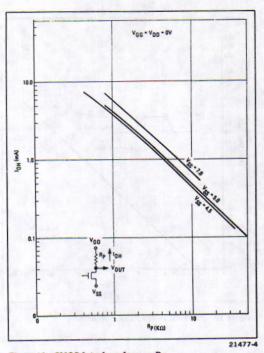

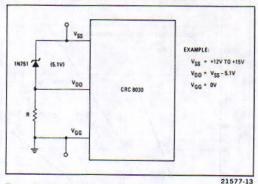

CRC 8000, CRC 8001 Binary-to-Dial Pulse Dialer CRC 8030 Dual Tone Multi-Frequency Detector CRC 8030 Application Note CRC 8030 Front-End Components

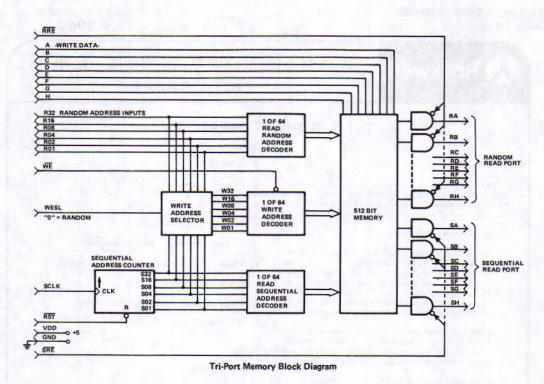

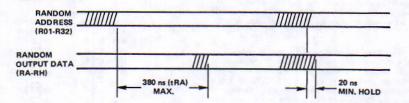

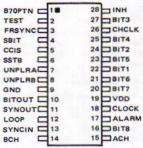

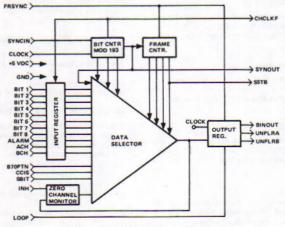

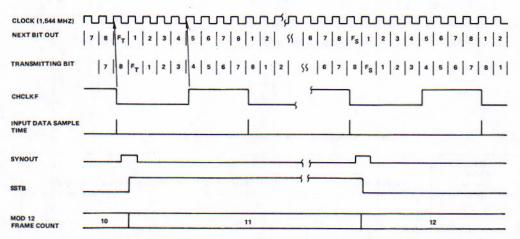

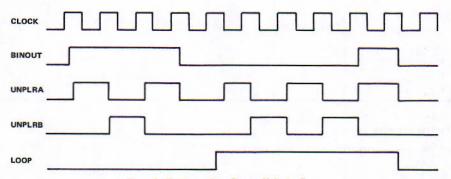

R8040 T-1 Tri-Port Memory R8050 T-1 Serial Transmitter R8060 T-1 Serial Receiver

# R6500 Family Brochure

# R6500 MICROCOMPUTER SYSTEM

R6500 NMOS PRODUCTS

# The R6500 Family

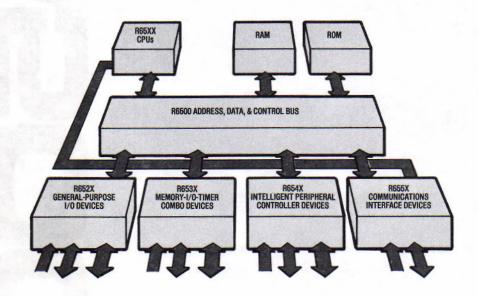

#### R6500 Family

A family of 10 software-compatible CPUs and 11 I/O, ROM, RAM and one-chip memory-I/O-timer circuits operating at proven 1 MHz and 2 MHz speeds with a single 5V power supply, provides you with economic system solutions for a broad range of applications.

The R6500/1 provides you with CPU, ROM, RAM, interrupts, counter and bi-directional data ports on a single chip. And it's totally software compatible with all other members of the R6500 family.

The R6500 promises you boosted performance and improved economics through its third generation architecture, which includes 13 powerful addressing modes, and its innovative circuit design and processing technology which reduce chip size and power consumption.

# Rockwell is solidly backing the R6500

Rockwell has dedicated facilities for the high volume manufacturing of R 6500 circuits produced with its own depletion load, silicon-gate N-channel process.

And Rockwell provides complete system development support: Rockwell's SYSTEM 65, a floppy-disk based, powerful yet low-cost complete development system. Plus AIM 65, TIM or timesharing program, complete documentation and extensive applications engineering support. For the future, Rockwell is developing new R6500 devices that will enhance your own product development opportunities.

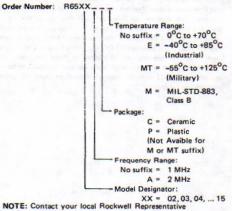

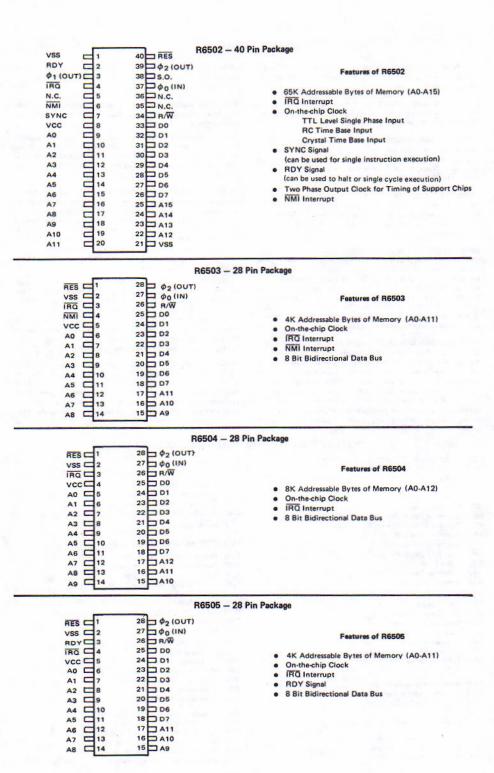

Rockwell's R650X CPU options offer a selection of features in 40- and 28-pin versions to meet your system needs (see table below). The R6502 - R6507 Series has on-chip clock generation. The R6512 - R6515 Series allows the user to generate and control the clock externally.

# Why the R6500 is a cost performance winner

- Proven 1 MHz or 2 MHz performance

- Pipeline architecture for fast operation with fewer cycles

- Single 5-volt power supply

- On-the-chip clock or an external clock

- 56 instructions

- 13 addressing modes and true indexing capability

- Decimal/binary arithmetic mode selection

- Bi-directional Data Bus (compatible with the MC 6800)

- Addressable memory range up to 65K bytes

- Multi-level interrupts maskable/non-maskable

- Use with any type or speed memory

- Programmable stack pointer and variable length stack

- 40- and 28-pin DIP package options

### **R6500 CPU Options**

|                                                 | 40-Pi      | n DIP      |                |                | 28-Pin DIP     |           |          |

|-------------------------------------------------|------------|------------|----------------|----------------|----------------|-----------|----------|

|                                                 | R6502      | R6512      | R6503<br>R6513 | R6504<br>R6514 | R6505<br>R6515 | R6506     | R6507    |

| Memory Address Space                            | 65K        | 65K        | 4K             | 8K             | 4K             | 4K        | 8K       |

| Interrupts — Maskable — Non-Maskable            | Yes<br>Yes | Yes<br>Yes | Yes<br>Yes     | Yes<br>No      | Yes<br>No      | Yes<br>No | No<br>No |

| SYNC—Output indicates op code fetch cycle       | Yes        | Yes        | No             | No             | No             | No        | No       |

| RDY—Single step and slow memory synchronization | Yes        | Yes        | No             | No             | Yes            | No        | Yes      |

| Ø <sub>1</sub> Clock Output                     | Yes        | Yes        | No             | No             | No             | Yes       | No       |

| DBE—Extended Data<br>Bus Hold Time              | No         | Yes        | No             | No             | No             | No        | No       |

The 40-pin versions provide full functional capability for memory intensive systems with extensive I/O requirements. The 28-pin versions offer flexibility in

selecting the lowest cost CPU best suited to your application. 28-pin packages also provide denser board layout.

### Thirteen addressing modes + true indexing = R6500 software power

The R 6500 features 13 addressing modes. The first byte of each instruction is the operation code specifying both the instruction and the addressing mode. The addressing modes are summarized below.

- ACCUMULATOR ADDRESSING A one byte instruction, operating on the accumulator.

- IMMEDIATE ADDRESSING The operand is in the second byte of the instruction.

- ABSOLUTE ADDRESSING The second and third bytes of the instruction specify the effective address in 65K bytes of addressable memory.

- ZERO PAGE ADDRESSING Allows shorter code and execution times by assuming a zero page address.

- INDEXED ZERO PAGE ADDRESSING (X or Y, indexing.) Zero page addressing used with an index register.

- INDEXED ABSOLUTE ADDRESSING (X or Y, indexing) — Absolute addressing used with X or Y index registers.

- IMPLIED ADDRESSING The register containing the operand is implicitly stated in the operation code.

- RELATIVE ADDRESSING Used only with branch instructions. The second byte is an "Offset" added to the contents of the program counter.

- INDEXED INDIRECT ADDRESSING Uses an indirect zero page address indexed by X to fetch the effective address.

- INDIRECT INDEXED ADDRESSING Uses a zero page address to fetch the effective base address to be indexed by Y.

- ABSOLUTE INDIRECT Used only with JMP, the second and third bytes point to a two-byte effective address.

# R6500 Microprocessor Instruction Set

Execution Time (clock cycles)

|       |      | S       |

|-------|------|---------|

| R6500 | NMUS | PRODUCT |

|     |                                                                             | Accumulat | Immediate | Zero Page | Zero Page, | Zero Page, | Absolute | Absolute, 3 | Absolute, | Implied | Relative | (Indirect, | (Indirect), | Absolute Ir |

|-----|-----------------------------------------------------------------------------|-----------|-----------|-----------|------------|------------|----------|-------------|-----------|---------|----------|------------|-------------|-------------|

| ADC | Add Memory to Accumulator with Carry                                        | :         | 2 2       | 3         | 4          | :          | 4        | 4*          | 4.        | :       | :        | 6          | 5°          | :           |

| ASL | "AND" Memory with Accumulator<br>Shift Left One Bit (Memory or Accumulator) | 2         | •         | 5         | 6          | •          | 6        | 7           | •         | :       |          | •          |             | ·           |

| BCC | Branch on Carry Clear                                                       |           |           |           |            |            |          |             |           |         | 2**      |            |             |             |

| BCS | Branch on Carry Set                                                         | •         | •         |           | •          |            |          | •           | •         | •       | 2**      |            | •           | •           |

| BEQ | Branch on Result Zero                                                       | •         | •         | •         | •          | •          | •        | •           | •         | •       | 2**      |            | •           | •           |

| BIT | Test Bits in Memory with Accumulator                                        | •         |           | 3         | :          | •          | 4        | :           | :         | :       | 2**      | :          | :           | :           |

| BMI | Branch on Result Minus                                                      | :         | :         | :         | :          | :          | :        | :           |           | :       | 2**      |            |             | :           |

| BNE | Branch on Result not Zero<br>Branch on Result Plus                          |           |           |           | :          |            | :        |             |           |         | 2**      |            |             |             |

| BRK | Force Break                                                                 |           |           |           |            |            |          |             |           |         |          |            |             |             |

| BVC | Branch on Overflow Clear                                                    | •         | •         |           | •          | •          |          |             | •         |         | 2**      |            | •           |             |

| BVS | Branch on Overflow Set                                                      | •         | •         | •         | •          | •          | •        | •           | •         | •       | 2**      | •          | •           | •           |

| CLC | Clear Carry Flag                                                            |           |           |           | •          |            |          | •           | •         | 2       |          |            |             |             |

| CLD | Clear Decimal Mode                                                          | •         | •         | •         | •          | •          | •        | •           | •         | 2       | •        | •          | •           | •           |

| CLI | Clear Interrupt Disable Bit                                                 | •         | •         | :         | •          | •          | •        | :           | :         | 2       | :        | •          | :           | :           |

| CLV | Clear Overflow Flag Compare Memory and Accumulator                          | :         | 2         | 3         | 4          | :          | 4        | 4.          | 4*        | -       | :        | 6          | 5*          | :           |

| CPX | Compare Memory and Index X                                                  | :         | 2         | 3         | •          |            | 4        |             | -         |         |          | •          |             |             |

| CPY | Compare Memory and Index Y                                                  |           | 2         | 3         | •          | •          | 4        | •           | •         |         | •        | •          | •           | •           |

| DEC | Decrement Memory by One                                                     |           |           | 5         | 6          |            | 6        | 7           |           |         |          |            |             |             |

| DEX | Decrement Index X by One                                                    |           |           |           |            |            |          | •           |           | 2       |          | •          |             |             |

| DEY | Decrement Index Y by One                                                    | •         |           | •         | •          | •          |          | •           | •         | 2       | •        | •          | •           | •           |

| EOR | "Exclusive OR" Memory with Accumulator                                      | •         | 2         | 3         | 4          | •          | 4        | 4*          | 4*        | •       | •        | 6          | 5           | •           |

| INC | Increment Memory by One                                                     |           | •         | 5         | 6          | •          | 6        | 7           | •         | •       | •        | •          | •           | •           |

| INX | Increment Index X by One                                                    | •         | •         | •         | •          | •          | •        | •           | •         | 2       | •        | •          | •           | •           |

| INY | Increment Y by One                                                          | •         | •         | •         | •          | •          | •        | •           | •         | 2       | •        | •          | •           | •           |

| JMP | Jump to New Location                                                        | •         |           | •         | •          | •          | 3        | •           | •         | •       | •        | •          | •           | 5           |

| JSR | Jump to New Location saving Return Address                                  | •         | •         | •         | •          | •          | 6        | •           | •         | •       |          | •          |             | •           |

| LDA | Load Accumulator with Memory                                                |           | 2         | 3         | 4          |            | 4        | 4*          | 4*        |         |          | 6          | 5*          |             |

| LDX | Load Index X with Memory                                                    |           | 2         | 3         | •          | 4          | 4        | •           | 4*        |         |          | •          |             |             |

| LDY | Load Index Y with Memory                                                    | •         | 2         | 3         | 4          | •          | 4        | 4*          | •         | •       | •        | •          | •           | •           |

| LSR | Shift Right One Bit (Memory or Accumulator)                                 | 2         | •         | 5         | 6          | •          | 6        | 7           | •         | •       | •        | •          | •           | •           |

| NOP | No Operation                                                                | •         |           |           | •          | •          |          | •           | •         | 2       |          | •          | •           | •           |

| ORA | "OR" Memory with Accumulator                                                | •         | 2         | 3         | 4          | •          | 4        | 4*          | 4*        | •       | •        | 6          | 5*          | •           |

| PHA | Push Accumulator on Stack                                                   | •         |           |           | •          | •          |          | •           | •         | 3       |          | •          |             |             |

| PHP | Push Processor Status on Stack                                              | •         | :         | •         | •          | •          |          | •           | •         | 3       | •        | •          | •           | •           |

| PLA | Pull Accumulator from Stack Pull Processor Status from Stack                | :         | :         | :         | :          | :          | :        | :           | :         | 4       | :        | :          | :           | :           |

| ROL | Rotate One Bit Left (Memory or Accumulator)                                 | 2         |           | 5         | 6          |            | 6        | 7           |           |         |          |            |             |             |

| ROR | Rotate One Bit Right (Memory or Accumulator)                                | 2         | :         | 5         | 6          | :          | 6        | 7           | :         | :       | :        | :          | :           | :           |

| RTI | Return from Interrupt                                                       |           |           |           |            |            |          |             |           | 6       |          |            |             |             |

| RTS | Return from Subroutine                                                      | •         | •         | •         | •          | •          | •        | •           | •         | 6       | •        | •          |             | •           |

| SBC | Subtract Memory from Accumulator with Borrow                                |           | 2         | 3         | 4          |            | 4        | 4*          | 4*        |         |          | 6          | 5*          |             |

| SEC | Set Carry Flag                                                              |           |           |           |            |            |          |             |           | 2       |          |            |             |             |

| SED | Set Decimal Mode                                                            | •         |           | •         | •          | •          |          |             | •         | 2       |          | •          |             | •           |

| SEI | Set Interrupt Disable Status                                                | •         | •         | •         | •          | •          | :        | :           | •         | 2       |          | •          | •           | •           |

| STA | Store Accumulator in Memory                                                 | :         | :         | 3         | 4          | 4          | 4        | 5           | 5         | •       | :        | 6          | 6           | •           |

| STX | Store Index X in Memory<br>Store Index Y in Memory                          | :         | :         | 3         | 4          | •          | 4        | :           | :         | :       | :        | :          | :           | :           |

| TAX | Transfer Accumulator to Index X                                             |           |           |           |            |            |          |             |           | 2       |          |            |             |             |

| TAY | Transfer Accumulator to Index Y                                             |           | •         |           |            |            |          |             | •         | 2       |          | •          |             |             |

| TSX | Transfer Stack Pointer to Index X                                           |           | •         |           | •          | •          |          | •           | •         | 2       |          | •          | •           |             |

| TXA | Transfer Index X to Accumulator                                             | •         |           | •         | •          | •          |          | •           | •         | 2       | •        | •          | •           |             |

| TXS | Transfer Index X to Stack Pointer Transfer Index Y to Accumulator           | •         | •         | •         | •          | •          | •        | •           | •         | 2       | •        | •          | •           | •           |

| ITA | Transfer Index Y to Accumulator                                             | •         | •         | •         | •          | •          | •        | •           | •         | 2       | •        | •          | •           | •           |

|     |                                                                             |           |           |           |            |            |          |             |           |         |          |            |             |             |

<sup>\*</sup>Add one cycle if Indexing across page boundary

\*\*Add one cycle if branch is taken, and one additional cycle if branching operatic crosses page boundary

### R6500 NMOS PRODUCTS

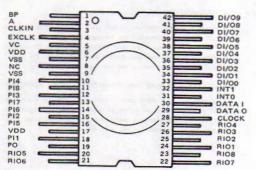

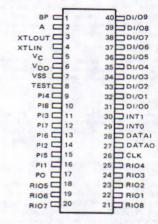

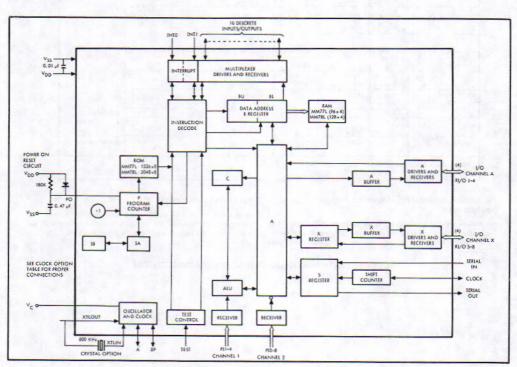

# R6500/1 One-Chip Microcomputer

#### The R6500/1

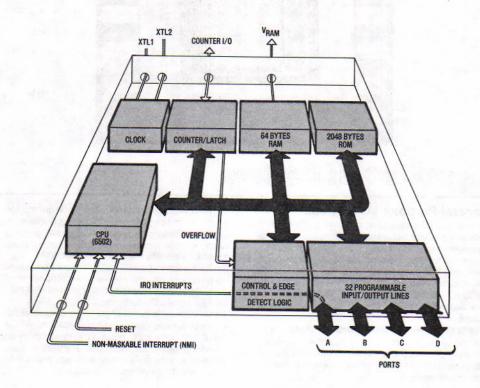

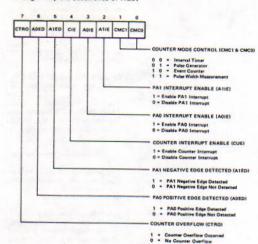

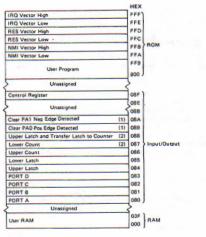

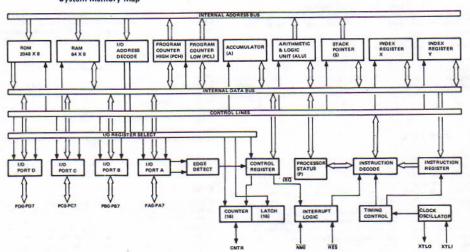

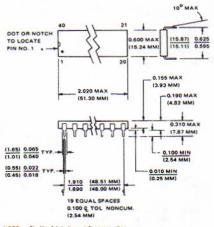

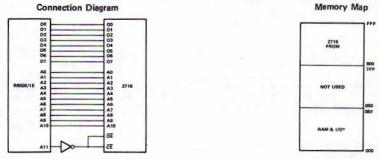

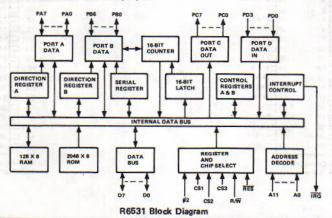

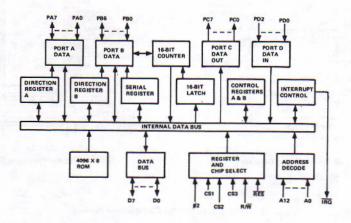

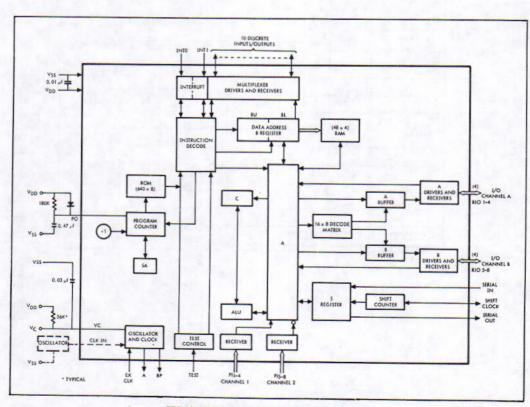

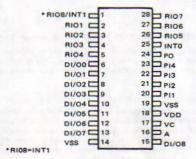

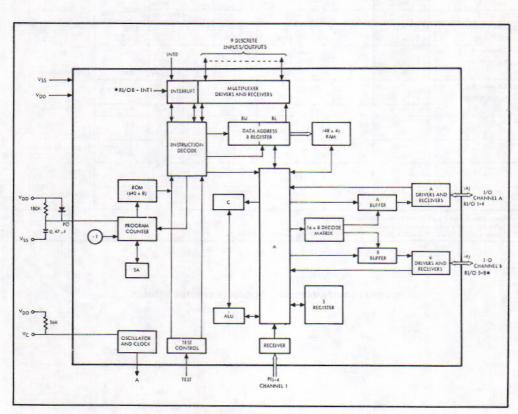

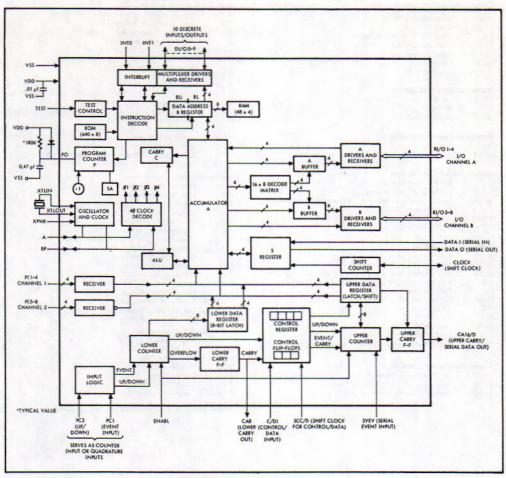

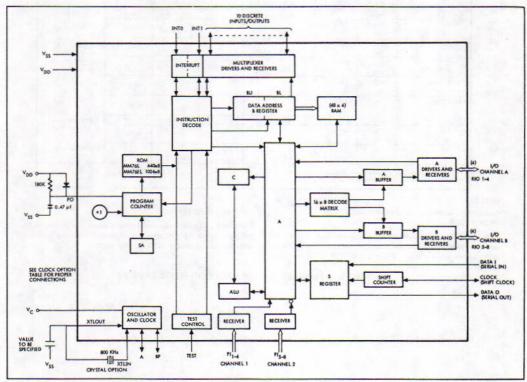

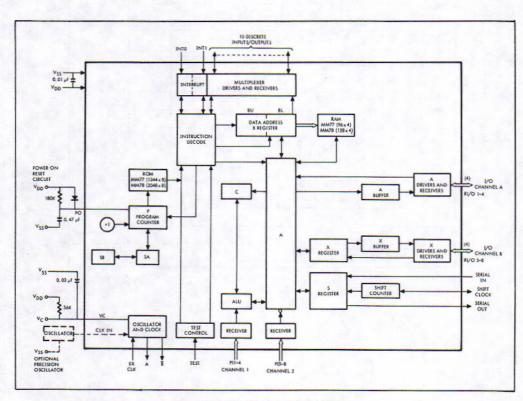

In the R6500/1, Rockwell has combined the highperformance R6502 CPU with such versatile features as 2048 bytes of ROM, 64 bytes of RAM, 32 bi-directional I/O lines, four interrupts and a 16-bit programmable counter (with four separate interval/event modes) — all in a single 40-bin package.

The R6500/1 also has on-the-chip 1 MHz or 2 MHz clock operation with external single clock, crystal or RC frequency input.

The R6500/1 includes a separate power pin that maintains RAM on 10% of the operating power. In the event power is lost, this standby power retains RAM data until execution is resumed.

Rockwell backs up the R6500/1 with solid system development support in two ways:

The R6500/1E, a 64-pin emulator device with 40 pins electrically identical to the R6500/1, may be used for program development and prototyping with external EPROM or RAM.

A Personality option to SYSTEM 65 customizes Rockwell's popular microcomputer development system for complete R6500/1 software and hardware development.

#### R6500/1 Features

- 2K-Byte Mask Programmable ROM

- 64-Byte Static RAM

- R6502 CPU

- Four 8-Bit Bidirectional I/O Ports

- 16-Bit Programmable Counter/Latch With Four Modes:

- Interval Timer

- Pulse Generator

- Event Counter

- Pulse Width Measurement

- Five Interrupts

- Fully Upward/Downward Compatible With 6500 Family

- 64-Pin PROM-compatible Emulator Device Available

# Standard Memory Devices

The R6500 system bus enables you to use low cost, widely available standard memory devices. For your convenience, Rockwell now offers the five memory devices, described below. All are completely TTL compatible, fully static — no clocks or refresh strobes required — and operate from a single +5 V power supply

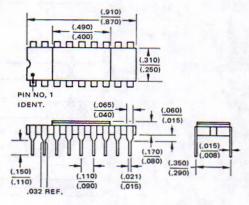

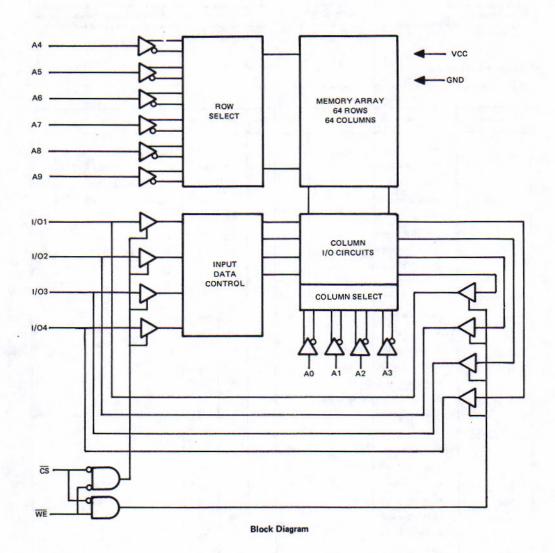

#### R2114 4K STATIC RAM

1024 x 4 in high-density 18-pin package with common data I/O; 450ns access and cycle time; fully static — no clocks or strobes required; single + 5V power supply; total TTL compatibility. (Industry standard.)

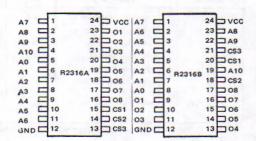

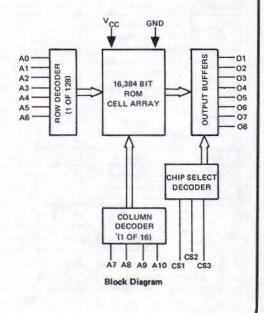

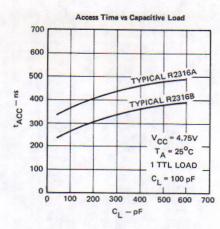

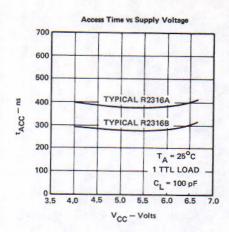

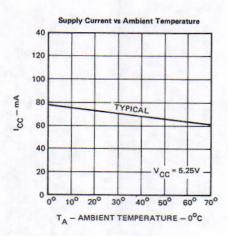

#### R2316B 16K STATIC ROM

2048 x 8 in standard 24-pin package; pin-compatible with 2708 EPROM; 450 ns. max. cycle time; three chip selects. (Industry standard; replaces *two* 8K EPROMs.)

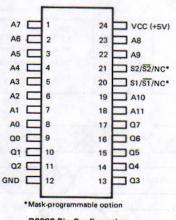

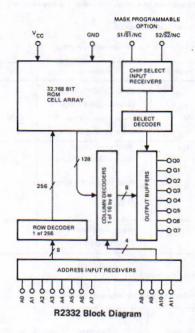

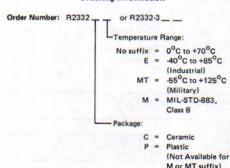

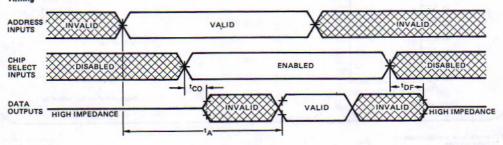

#### R2332 32K STATIC ROM

The industry's first static 4096 x 8 N-channel ROM; standard 24-pin package; 450 ns. max. cycle time; two chip selects.

#### R2332-3 32K STATIC ROM

Same as R2332, but has 300 ns. max. cycle time.

# Input/Output Devices

#### General-Purpose I/O Devices

These versatile peripheral controllers allow effective trade-offs between software and hardware, enabling implementation of complex R6500 microcomputer systems at minimum overall cost. Both are available in 1 MHz and 2 MHz versions. All R6500 I/O devices—including the memory-I/O combos—have TTL and CMOS compatible peripheral lines with transistor drive capability and high-impedance, tri-state data

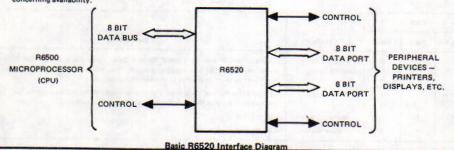

#### R6520 Peripheral Interface Adapter (PIA)

40-pin package, two 8-bit bi-directional I/O ports, four peripheral control/interrupt input lines, fully automatic data transfers between processor and peripheral devices.

The PIA provides individual I/O line control for keyboard strobes and returns, driving displays and discrete indicators as well as 8-bit parallel communications in handshake or clocked control modes.

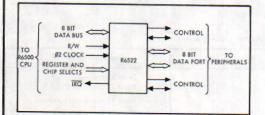

#### R6522 Versatile Interface Adapter (VIA)

40-pin package, has R 6520 PIA features plus two 16-bit programmable interval timers/counters, data latching on I/O ports, 8-bit buffered shift register for serial I/O interfacing.

The enhanced features of the VIA provide a serial interface for inter-system communications, ASCII serial data generation, pulse width modulation, and waveform synthesis. The two timers work in conjunction with the serial channel or may provide interval timing for real time applications.

### R6500 NMOS PRODUCTS

# Input/Output Devices

#### Memory-I/O-Timer Combination Devices

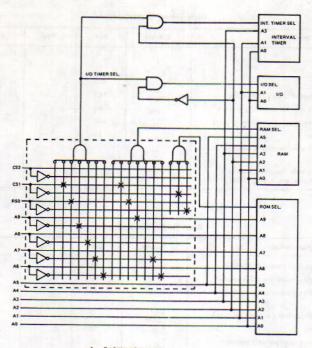

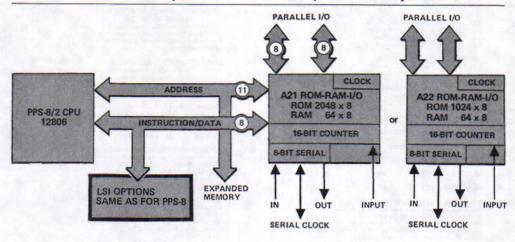

By combining an R650X Series CPU with one-chip memory, I/O and timer combination devices, the designer nets a powerful, cost-effective two chip microcomputer system which can also be the base configuration for modular, expandable applications.

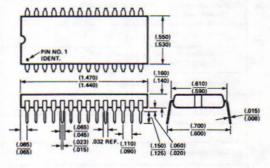

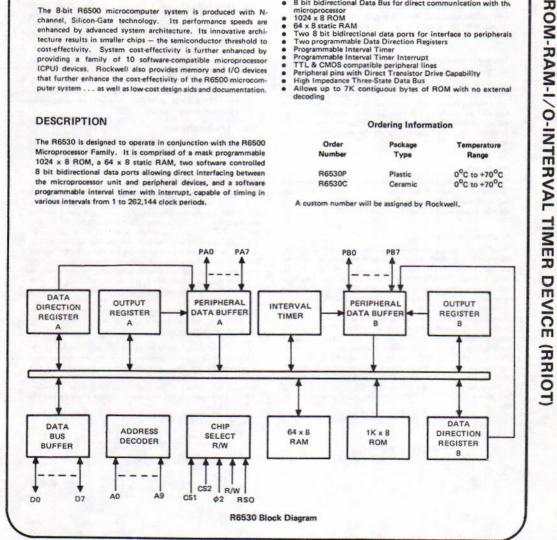

R6530 ROM-RAM-I/O-Timer (RRIOT)

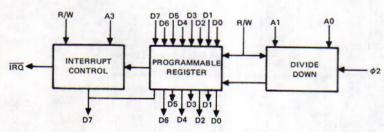

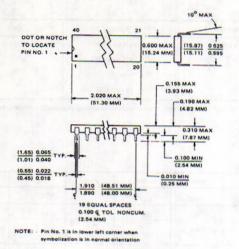

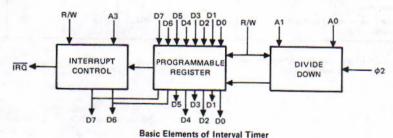

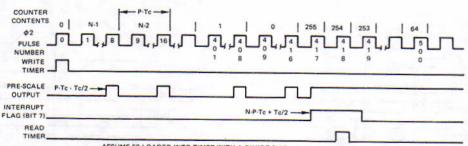

40-pin package; 1 MHz operation; 1024 x 8 ROM; 64 x 8 static RAM; two 8-bit bi-directional data I/O ports; two progammable data direction registers; programmable 8-bit interval timer with prescale and interrupt control.

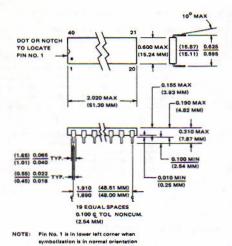

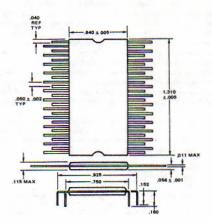

R6531 ROM-RAM-I/O-Counter (RRIOC)

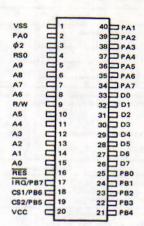

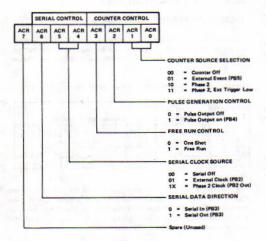

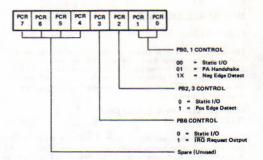

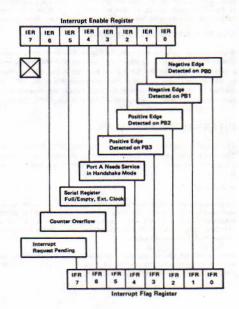

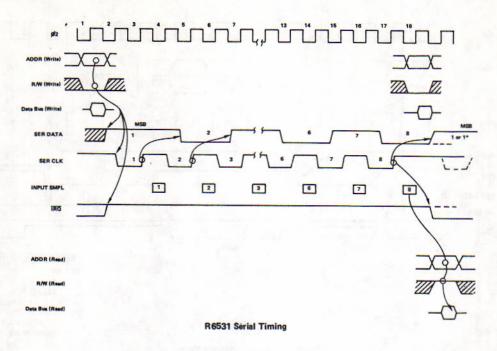

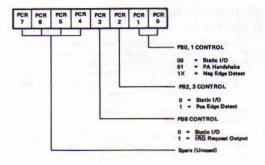

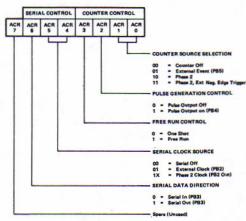

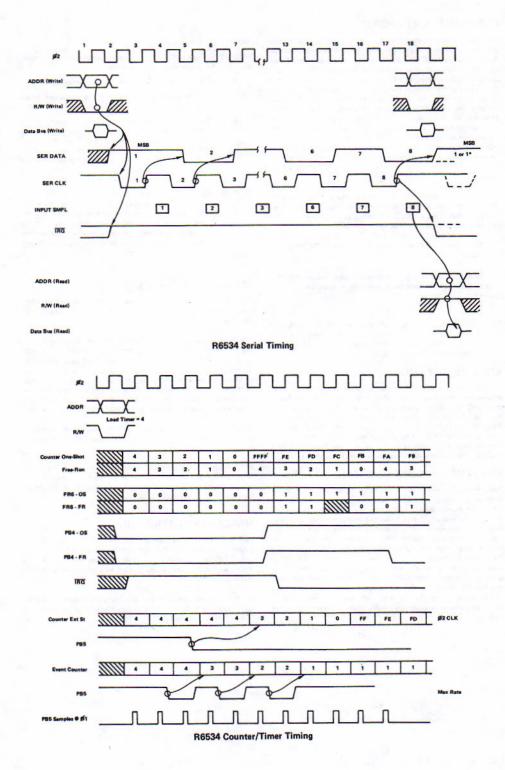

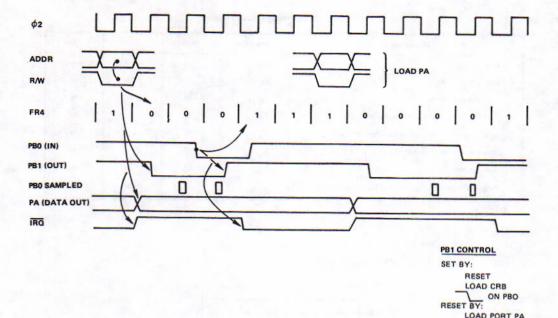

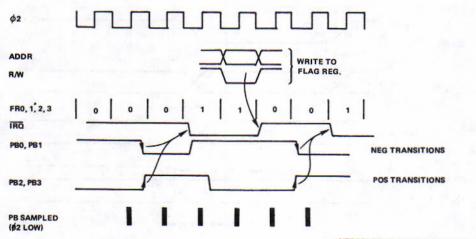

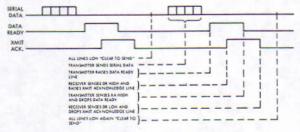

40-pin package; 1 MHz or 2 MHz operation; 2048 x 8 ROM; 128 x 8 static RAM; 8-bit serial data channel; two bi-directional I/O ports, with a total of 15 data lines, including four external interrupts and handshake control.

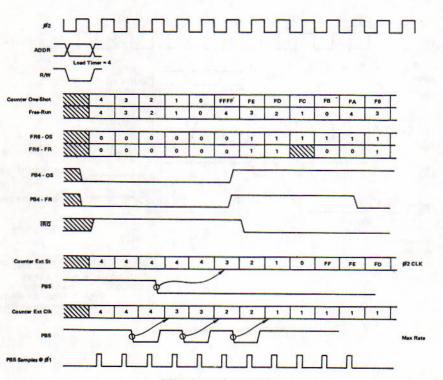

The RRIOC also provides a fully-buffered 16-bit counter/timer with four program selectable modes — interval timer, pulse generator, event counter and pulse width measurement.

A separate 52-pin version of RRIOC offers expanded I/O in additional 8-bit output port and 4-bit input port.

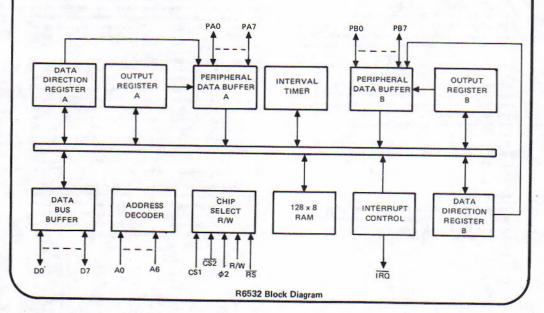

R6532 RAM-I/O-Timer (RIOT)

40-pin package; 1 MHz operation; 128 x 8 static RAM; two 8-bit bi-directional data ports; two programmable data direction registers; programmable 8-bit interval timer with prescale and interrupt control; programmable edge detect interrupt, for fast service of critical events.

R6534 ROM-I/O-Counter (RIOC)

40-pin package; 1 MHz operation; 4096 x 8 ROM; 8-bit serial data channel; two bi-directional data I/O ports, with a total of 14 data lines, including four external interrupts and handshake control.

The RIOC also provides a programmable 16-bit counter/latch with interval timer, pulse generator and event counter modes.

A separate 52-pin version of RIOC offers an additional 8-bit output port, 3-bit input port and one additional I/O line.

#### Intelligent Peripheral Controller Devices

The devices listed below get your interface design off to a solid start.

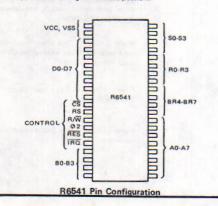

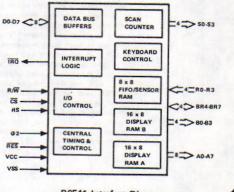

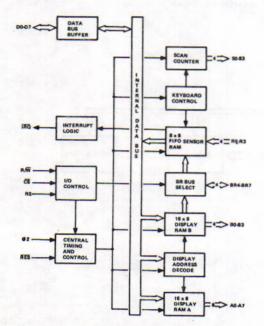

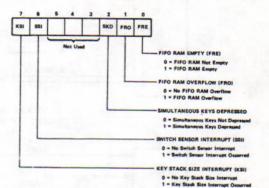

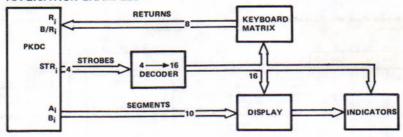

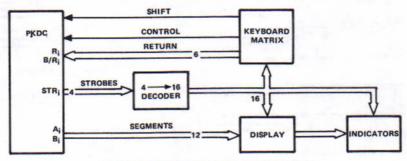

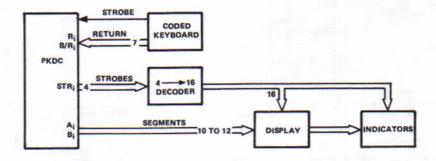

R6541 Programmable Keyboard/Display Controller (PKDC)

40-pin package, 8-character FIFO/Sensor RAM for keyboard entries, two CPU-addressable 16-byte display RAMs.

The PKDC is a general-purpose keyboard and segmented display interface device. The keyboard portion can scan up to 128 matrix-type key switches, and can also interface with an array of 64 sensors or a strobed interface keyboard. The display portion provides a

buffered scanned display interface with LED, fluorescent, Borroughs SELF-SCAN®, and other display technologies.

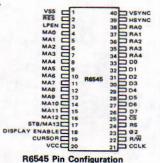

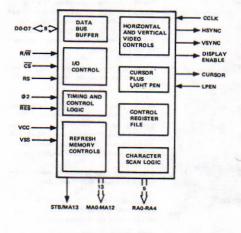

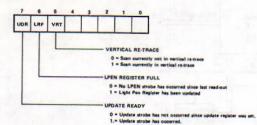

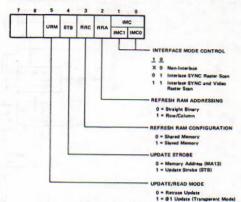

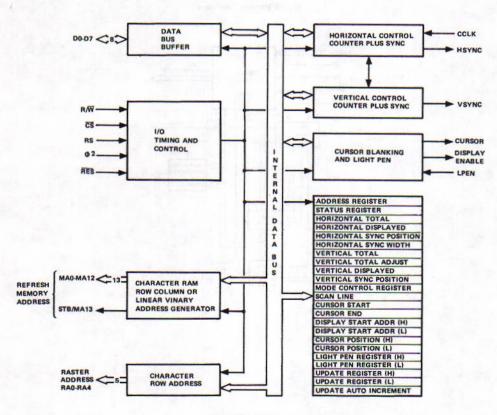

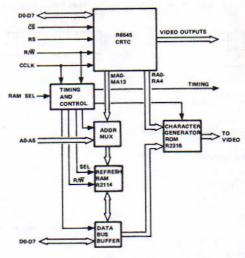

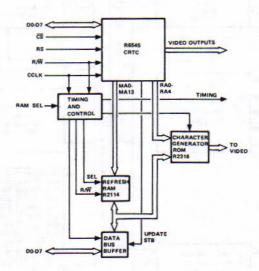

R6545 CRT Controller (CRTC)

40-pin package, refresh RAM, fully-programmable scanning and cursor, light pen register.

The CRTC is designed to interface an 8-bit microprocessor to CRT raster scan video displays. It provides refresh memory addresses and character generator row addresses, which allow up to 16K characters with 32 scan lines per character to be addressed. Refresh memory may be addressed in either straight binary or by row/column.

#### **Communications Interface Device**

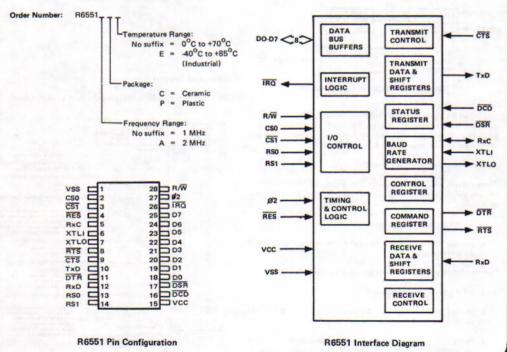

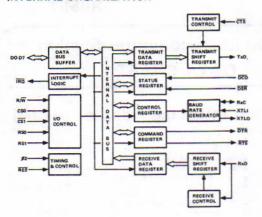

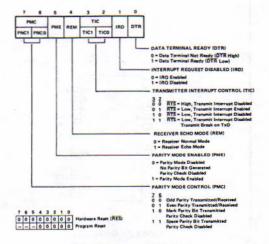

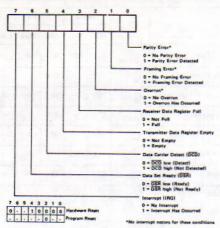

R6551 Asynchronous Communication Interface Adapter (ACIA)

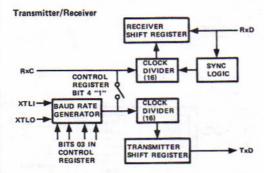

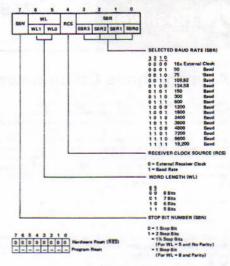

28-pin package provides the interface between R6500based systems and serial communication data sets and modems. With its on-chip baud rate generator, the ACIA is capable of transmitting at 15 different programselectable rates between 50 baud and 19,200 baud, and receiving at either the transmit rate or at 16X an external clock rate.

The ACIA has programmable word lengths of 5, 6, 7 or 8 bits; even, odd or no parity; 1, 1-1/2 or 2 stop bits.

# Product Development

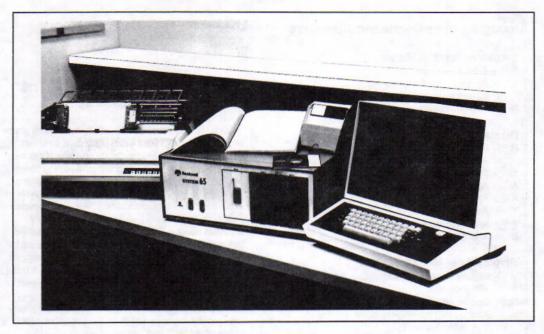

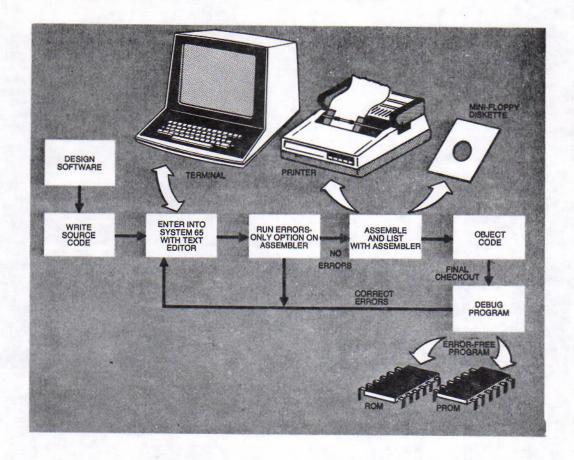

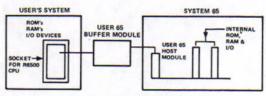

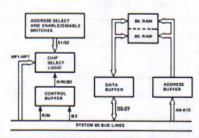

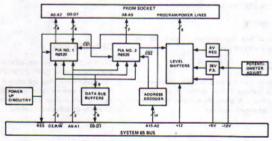

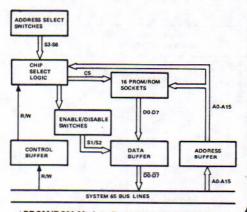

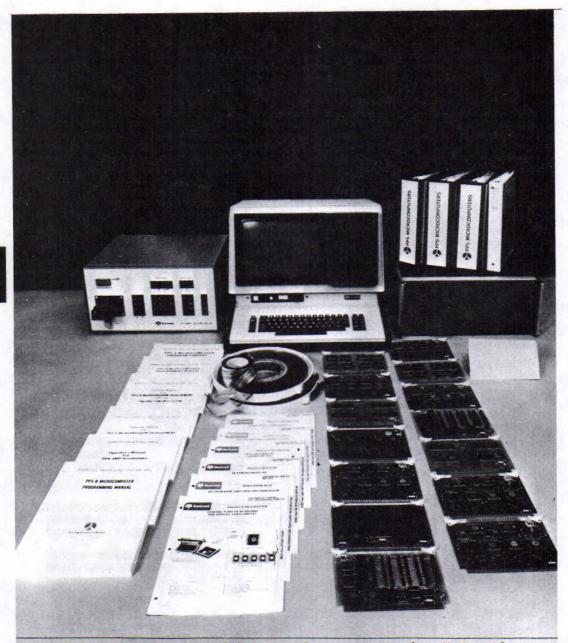

#### Rockwell's SYSTEM 65

SYSTEM 65 is a new easy to use, powerful, complete development system for the R6500 family of microcomputers. The basic configuration includes two built-in, mini-floppy disk drives, 16K bytes of user memory and 16K bytes of resident operating system.

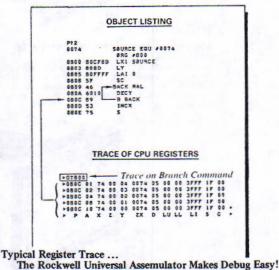

Monitor commands are self-prompting whenever memory, peripheral, or disk file assignment is required. Text editor provides line, string, and character editing functions. A resident two-pass assembler and dynamic debug package complete the operating system. Both source and object code may be maintained in memory for fast editing, assembling, and checkout. Since the total monitor, editor, debug and assembler are resident in ROM, 100% of the disk storage and drive utilization is available to the user.

The mini-floppy diskettes may be used as storage for source and object code and documentation. Each diskette has the capacity for 78K bytes of information in a maximum of 60 files.

SYSTEM 65 supports a vareity of terminals with serial data from 100 baud to 9600 baud. Connectors are provided for both RS-232 C and current loop interfacing. Reader ON/OFF signals and RTS/CTS control signals are standard. Included is a parallel port providing automatic control to high speed printers, such as Diablo, Centronics and Tally.

#### And Rockwell offers these options to SYSTEM 65:

- PL/65 High-Level Language

- · USER 65 in-circuit emulation option

- PROM Programmer Module, for programming a 2704/2708/2716/2758 PROM device from the front panel socket

- R6500/1 Personality option, for developing with the R6500/1 single-chip microcomputer

- 16K x 8 Static RAM Modules

- PROM/ROM Module, accepts 2316/2332 ROM or 2708/2716/2758 PROM devices

- Wire-wrap Design Prototyping Module

- · Extender Card for circuit probing

#### PL/65 High-Level Language

A high-level language resembling PL/1 and ALGOL is now available to designers developing programs for the R6500 microprocessor family using the SYSTEM 65 development system.

Designated PL/65, the language is considerably easier to use than assembly language or object code, thus increasing programmer productivity while reducing software development time and costs. The PL/65 compiler outputs source code to the SYSTEM 65's resident assembler. This permits enhancing or debugging at the assembler level before object code is generated. In addition, PL/65 statements may be mixed with assembly language instructions for timing or code optimization.

The PL/65 compiler is available to SYSTEM 65 users as a preprogrammed mini-floppy diskette. No additional memory is required other than the standard 16K bytes of RAM.

The PL/65 language supports modular program design. Its general control structures for conditional and iterative looping allow the language to be used effectively for structured programs. Other language features include: assignment, integer arithmetic, conditional execution, collective execution, linear array manipulation, data area declaration and array initialization. Block structures, subscripts and parenthetical expressions are also supported.

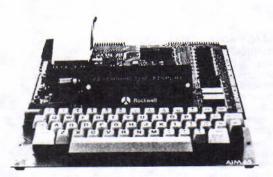

### For learning, designing, work or just plain fun....

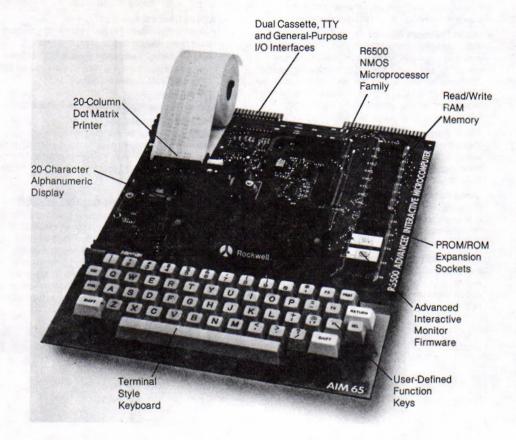

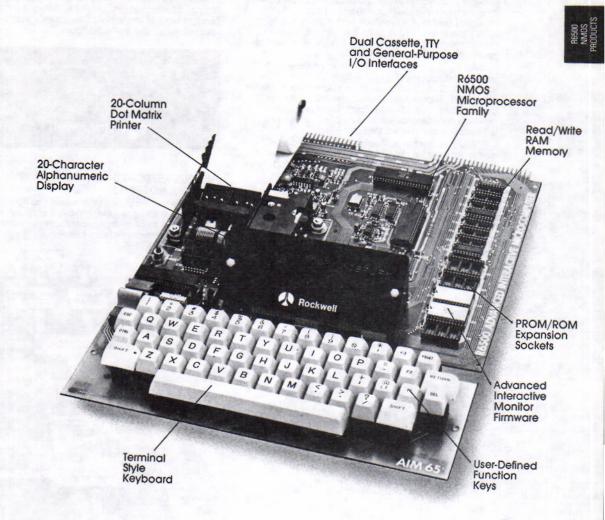

Rockwell's R6500 Advanced Interactive Microcomputer (AIM 65) can get you into the exciting world of microcomputers a lot easier and at a lot lower cost than you may have thought possible.

As a learning aid, AIM 65 gives you an assembled; tested and warranted R6502-based microcomputer system with a full-sized keyboard, an alphanumeric 20-character display and, uniquely, an alphanumeric 20-column thermal printer.

An on-board Advanced Interactive Monitor program provides extensive control and program development

functions. You'll be writing your programs in assembly language — there's no need to memorize "opcodes". And for more specialized applications, we offer a two-pass, symbolic assembler and a BASIC interpreter as plug-in ROM options.

You'll master fundamentals rapidly. Then you'll appreciate the fact that unlike the computer "toys" on the market, AIM 65 offers flexibility and expandability you would expect to find only in a sophisticated microcomputer development system.

## Literature

#### How to make it all work for you

Rockwell has put together a complete set of documentation and reference manuals to help you implement the R6500 microprocessor family.

#### R6500 Hardware Manual

A detailed description of each chip in the family, how they interface, how the peripherals are controlled, as well as the design techniques facilitating system operation, testing and maintenance. Special emphasis is on "bringing up" a system with testing techniques, scope synchronizing and general trouble-shooting procedures — \$5.

#### R6500 Programming Manual

Defines the architecture of the R6500 Series, the function of each instruction and valuable programming information. Special emphasis is on the sophisticated addressing modes of the family — \$5.

#### Cross-Assembler Manual

Cross-Assembler directives are described as used in time-share and batch operations, with special aids on understanding and resolving error messages — \$5.

#### SYSTEM 65 User's Manual

Instructs the user in operating the SYSTEM 65 Microcomputer Development System and its application in developing a working microprocessor system — \$5.

#### PL/65 User's Manual

A complete guide to PL/65, the high-level language for the R6500 family — \$10.

#### · AIM 65 User's Guide

Full technical details tell you everything you need to operate the AIM 65 — \$5.

# AIM 65 BASIC Language Reference Manual A how-to guide for using AIM 65 with the BASIC

A now-to guide for using AIM 65 with the BAI language ROM option installed—\$5.

#### TIM Manual

Defines how to apply the Teletype I/O Monitor — \$2.

#### R6500 Data Sheets

Provides quick understanding of the capabilities and characteristics of each available R6500 device and support equipment. To order data sheets simply specify the part number or the name of the support equipment.

#### Where to get more on the R6500

Rockwell's normal procedure is to provide you with free data sheets so that you can select the R6500 devices and support equipment of most interest to you. A nominal charge is made for reference manuals.

For data, devices or support equipment contact the nearest Rockwell office or distributor listed on the back page of this brochure. For in-depth assistance, obtain the name of your nearest Rockwell sales representative from any Rockwell office.

R6500 MICROPROCESSORS (CPU's

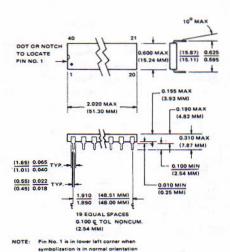

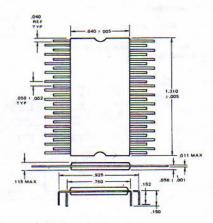

### R6500 Microcomputer System DATA SHEET

### R6500 MICROPROCESSORS (CPU's)

#### SYSTEM ABSTRACT

The 8-bit R6500 microcomputer system is produced with N-Channel, Silicon Gate technology. Its performance speeds are enhanced by advanced system architecture. This innovative architecture results in smaller chips - the semiconductor threshold to cost-effectivity. System cost-effectivity is further enhanced by providing a family of 10 software-compatible microprocessor (CPU) devices, described in this document. Rockwell also provides memory and microcomputer system . . . as well as low-cost design aids and documentation.

#### R6500 MICROPROCESSOR (CPU) CONCEPT

Ten CPU devices are available. All are software-compatible. They provide options of addressable memory, interrupt input, on-chip clock oscillators and drivers. All are bus-compatible with earlier generation microprocessors like the M6800 devices.

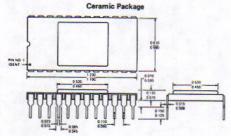

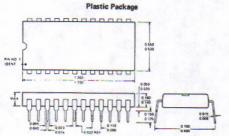

The family includes six microprocessors with on-board clock oscillators and drivers and four microprocessors driven by external clocks. The on-chip clock versions are aimed at high performance, low cost applications where single phase inputs, crystal or RC inputs provide the time base. The external clock versions are geared for multiprocessor system applications where maximum timing control is mandatory. All R6500 microprocessors are also available in a variety of packaging (ceramic and plastic), operating frequency (1 MHz and 2 MHz) and temperature (commercial, industrial and military) versions,

#### MEMBERS OF THE R6500 MICROPROCESSOR (CPU) FAMILY

Microprocessors with On-Chip Clock Oscillator

| Model | Addressable Memor |

|-------|-------------------|

| R6502 | 65K Bytes         |

| R6503 | 4K Bytes          |

| R6504 | 8K Bytes          |

| R6505 | 4K Bytes          |

| R6506 | 4K Bytes          |

| R6507 | 8K Bytes          |

|       |                   |

Microprocessors with External Two Phase Clock Output

| Model | Addressable Memory |

|-------|--------------------|

| R6512 | 65K Bytes          |

| R6513 | 4K Bytes           |

| R6514 | 8K Bytes           |

| R6515 | 4K Bytes           |

#### **FEATURES**

- Single +5V supply

- N channel, silicon gate, depletion load technology

- Eight bit parallel processing

- 56 Instructions

- Decimal and binary arithmetic

- Thirteen addressing modes

- True indexing capability

- Programmable stack pointer

- Variable length stack Interrupt capability

- Non-maskable interrupt

- Use with any type of speed memory

- 8-bit Bidirectional Data Bus

- Addressable memory range of up to 65K bytes

- "Ready" input

- Direct Memory Access capability

- Rus compatible with M6800

- 1 MHz and 2 MHz operation

- Choice of external or on-chip clocks

- On-the-chip clock options - External single clock input

- RC time base input

- Crystal time base input

- Commercial, industrial and military temperature versions

- Pipeline architecture

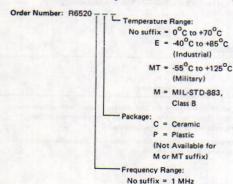

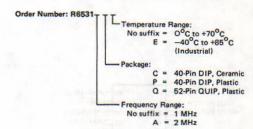

#### Ordering Information

concerning availability.

#### **R6500 Signal Description**

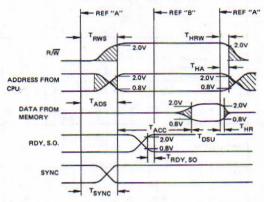

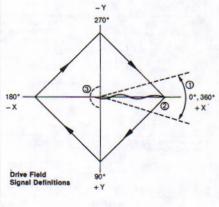

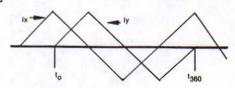

#### Clocks (\$\phi\_1, \$\phi\_2\$)

The R651X requires a two phase non-overlapping clock that runs at the  $\rm V_{CC}$  voltage level.

The R650X clocks are supplied with an internal clock generator. The frequency of these clocks is externally controlled.

#### Address Bus (A0-A15)

These outputs are TTL compatible, capable of driving one standard TTL load and 130 pF.

#### Data Bus (D0-D7)

Eight pins are used for the data bus. This is a bidirectional bus, transferring data to and from the device and peripherals. The outputs are tri-state buffers capable of driving one standard TTL load and 130 of.

#### Data Bus Enable (DBE)

This TTL compatible input allows external control of the tri-state data output buffers and will enable the microprocessor bus driver when in the high state. In normal operation DBE would be driven by the phase two  $(\phi_2)$  clock, thus allowing data output from microprocessor only during  $\phi_2$ . During the read cycle, the data bus drivers are internally disabled, becoming essentially an open circuit. To disable data bus drivers externally, DBE should be held low.

#### Ready (RDY)

This input signal allows the user to halt or single cycle the microprocessor on all cycles except write cycles. A negative transition to the low state during or coincident with phase one  $(\phi_1)$  will halt the microprocessor with the output address lines reflecting the current address being fetched. If Ready is low during a write cycle, it is ignored until the following read operation. This condition will remain through a subsequent phase two  $(\phi_2)$  in which the Ready signal is low. This feature allows microprocessor interfacing with the low speed PROMs as well as fast (max. 2 cycle) Direct Memory Access (DMA).

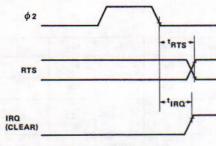

#### Interrupt Request (IRQ)

This TTL level input requests that an interrupt sequence begin within the microprocessor. The microprocessor will complete the current instruction being executed before recognizing the request. At that time, the interrupt mask bit in the Status Code Register will be examined. If the interrupt mask flag is not set, the microprocessor will begin an interrupt sequence. The Program Counter and Processor Status Register are stored in the stack. The microprocessor will then set the interrupt mask flag high so that no further interrupts may occur. At the end of this cycle, the program counter low will be loaded from address FFFE, and program counter high from location FFFF, therefore transferring program control to the memory vector located at these addresses. The RDY signal must be in the high state for any interrupt to be recognized. A 3KΩ external resistor should be used for proper wire-OR operation.

#### Non-Maskable Interrupt (NMI)

A negative going edge on this input requests that a non-maskable interrupt sequence be generated within the microprocessor.

$\overline{\text{NM}}$  is an unconditional interrupt. Following completion of the current instruction, the sequence of operations defined for  $\overline{\text{IRQ}}$  will be performed, regardless of the state interrupt mask flag. The vector address loaded into the program counter, low and high, are locations FFFA and FFFB respectively, thereby transferring program control to the memory vector located at these addresses. The instructions loaded at these locations cause the microprocessor to branch to a non-maskable interrupt routine in memory.

$\overline{\text{NMI}}$  also requires an external 3K  $\Omega$  register to  $V_{\overline{\text{CC}}}$  for proper wire-OR operations.

Inputs  $\overline{IRQ}$  and  $\overline{NMI}$  are hardware interrupts lines that are sampled during  $\phi_2$  (phase 2) and will begin the appropriate interrupt routine on the  $\phi_1$  (phase 1) following the completion of the current instruction.

#### Set Overflow Flag (S.O.)

A negative going edge on this input sets the overflow bit in the Status Code Register. This signal is sampled on the trailing edge of \$\phi\_1\$ and must be externally synchronized.

#### SYNC

This output line is provided to identify those cycles in which the microprocessor is doing an OP CODE fetch. The SYNC line goes high during  $\phi_1$  of an OP CODE fetch and stays high for the remainder of that cycle. If the RDY line is pulled low during the  $\phi_1$  clock pulse in which SYNC went high, the processor will stop in its current state and will remain in the state until the RDY line goes high. In this manner, the SYNC signal can be used to control RDY to cause single instruction execution.

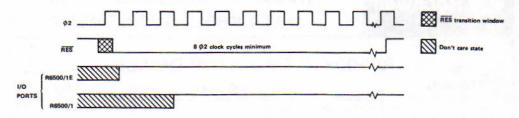

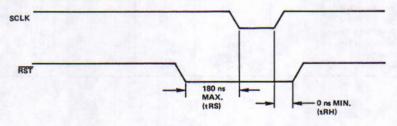

#### Reser

This input is used to reset or start the microprocessor from a power down condition. During the time that this line is held low, writing to or from the microprocessor is inhibited. When a positive edge is detected on the input, the microprocessor will immediately begin the reset sequence.

After a system initialization time of six clock cycles, the mask interrupt flag will be set and the microprocessor will load the program counter from the memory vector locations FFFC and FFFD. This is the start location for program control.

After  $V_{CC}$  reaches 4.75 volts in a power up routine, reset must be held low for at least two clock cycles. At this time the R/W and (SYNC) signal will become valid,

When the reset signal goes high following these two clock cycles, the microprocessor will proceed with the normal reset procedure detailed above.

#### ADDRESSING MODES

ACCUMULATOR ADDRESSING - This form of addressing is represented with a one byte instruction, implying an operation on the accumulator.

IMMEDIATE ADDRESSING - In immediate addressing, the operand is contained in the second byte of the instruction, with no further memory addressing required.

ABSOLUTE ADDRESSING - In absolute addressing, the second byte of the instruction specifies the eight low order bits of the effective address while the third byte specifies the eight high order bits. Thus, the absolute addressing mode allows access to the entire 65K bytes of addressable memory.

ZERO PAGE ADDRESSING - The zero page instructions allow for shorter code and execution times by only fetching the second byte of the instruction and assuming a zero high address byte. Caroful use of the zero page can result in significant increase in

INDEXED ZERO PAGE ADDRESSING - (X, Y indexing) - This form of addressing is used in conjunction with the index register and is referred to as "Zero Page, X" or "Zero Page, Y". The effective address is calculated by adding the second byte to the contents of the index register. Since this is a form of "Zero Page" addressing, the content of the second byte references a location in page zero. Additionally due to the "Zero Page" addressing nature of this mode, no carry is added to the high order 8 bits of memory and crossing of page boundaries does not occur.

INDEXED ABSOLUTE ADDRESSING - (X, Y indexing) - This form of addressing is used in conjunction with X and Y index register and is referred to as "Absolute, X", and "Absolute, Y". The effective address is formed by adding the contents of X or Y to the address contained in the second and third bytes of the instruction. This mode allows the index register to contain the index or count value and the instruction to contain the base address. This type of indexing allows any location referencing and the index to modify multiple fields resulting in reduced coding and execution time.

IMPLIED ADDRESSING - In the implied addressing mode, the address containing the operand is implicitly stated in the operation code of the instruction.

RELATIVE ADDRESSING - Relative addressing is used only with branch instructions and establishes a destination for the conditional branch.

The second byte of the instruction becomes the operand which is an "Offset" added to the contents of the lower eight bits of the program counter when the counter is set at the next instruction. The range of the offset is -128 to +127 bytes from the next instruction

INDEXED INDIRECT ADDRESSING - In indexed indirect addressing (referred to as (Indirect, X)), the second byte of the instruction is added to the contents of the X index register, discarding the carry. The result of this addition points to a memory location on page zero whose contents is the low order eight bits of the effective address. The next memory location in page zero contains the high order eight bits of the effective address. Both memory locations specifying the high and low order bytes of the effective address must be in page zero.

INDIRECT INDEXED ADDRESSING - In indirect indexed addressing (referred to as (Indirect), Y), the second byte of the instruction points to a memory location in page zero. The contents of this memory location is added to the contents of the Y index register, the result being the low order eight bits of the effective address. The carry from this addition is added to the contents of the next page zero memory location, the result being the high order eight bits of the effective address.

ABSOLUTE INDIRECT - The second byte of the instruction contains the low order eight bits of a memory location. The high order eight bits of that memory location is contained in the third byte of the instruction. The contents of the fully specified memory location is the low order byte of the effective address. The next memory location contains the high order byte of the effective address which is loaded into the sixteen bits of the program counter.

#### INSTRUCTION SET - ALPHABETIC SEQUENCE

- ADC Add Memory to Accumulator with Carry

- AND "AND" Memory with Accumulator ASL Shift left One Bit (Memory or Accumulator)

- BCC Branch on Carry Clear

- BCS Branch on Carry Set

- REO Branch on Result Zero

- BIT Test Bits in Memory with Accumulator

- BMI Branch on Result Minus

- BNE Branch on Result not Zero

- **BPL** Branch on Result Plus

- BRK Force Break

- **BVC** Branch on Overflow Clear

- **BVS** Branch on Overflow Set

- CLC Clear Carry Flag

- **CLD** Clear Decimal Mode

- CLI Clear Interrupt Disable Bit CLV Clear Overflow Flag

- CMP Compare Memory and Accumulator

- CPX Compare Memory and Index X

- Compare Memory and Index Y

- DEC Decrement Memory by One

- DEX Decrement Index X by One

- DEY Decrement Index Y by One

- EOR "Exclusive-or" Memory with Accumulator

- INC Increment Memory by One

- INX Increment Index X by One Increment Index Y by One INY

- Jump to New Location

- ISB Jump to New Location Saving Return Address

- LDA Load Accumulator with Memory

- LDX Load Index X with Memory LDY Load Index Y with Memory

- LSR Shift One Bit Right (Memory or Accumulator)

- NOP No Operation

- ORA "OR" Memory with Accumulator

- PHA Push Accumulator on Stack

- PHP Push Processor Status on Stack PLA Pull Accumulator from Stack

- Pull Processor Status from Stack PIP

- ROL Rotate One Bit Left (Memory or Accumulator)

- ROR Rotate One Bit Right (Memory or Accumulator) RTI Return from Interrupt

- RTS Return from Subroutine

- SBC Subtract Memory from Accumulator with Borrow

- SEC Set Carry Flag

- SED Set Decimal Mode

- SEI Set Interrupt Disable Status

- STA Store Accumulator in Memory

- STX Store Index X in Memory

- Store Index Y in Memory STY

- TAX Transfer Accumulator to Index X

- TAY Transfer Accumulator to Index Y

- TSX Transfer Stack Pointer to Index X

- TXA Transfer Index X to Accumulator TXS Transfer Index X to Stack Register

- TYA Transfer Index Y to Accumulator

| RES  | 3    | 1  | 28 | □ φ <sub>2</sub> (OUT) |

|------|------|----|----|------------------------|

| VSS  |      | 2  | 27 | □φ <sub>0</sub> (IN)   |

| Ø1 ( | OUT) | 3  | 26 | □R/W                   |

| IRO  |      | 4  | 25 | D 00                   |

| VCC  |      | 5  | 24 | □ D1                   |

| AO   |      | 6  | 23 | □ D2                   |

| A1   |      | 7  | 22 | 5 p3                   |

| A2   |      | 8  | 21 | D4                     |

| A3   |      | 9  | 20 | D4                     |

| A4   |      | 10 | 19 |                        |

| A5   |      | 11 | 18 | D6                     |

| A6   |      | 12 | 17 | A11                    |

| A7   |      | 13 | 16 | A10                    |

| A8   |      | 14 | 15 | □ A9                   |

|      |      |    |    |                        |

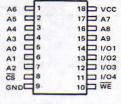

#### Features of R6506

- 4K Addressable Bytes of Memory (A0-A11)

- · On-the-chip Clock

- e IRQ Interrupt

- Two phase output clock for timing of support chips

- 8 Bit Bidirectional Data Bus

#### R6507 - 28 Pin Package

#### Features of R6507

- 8K Addressable Bytes of Memory (A0-A12)

- On-the-chip Clock

- RDY Signal

- 8 Bit Bidirectional Data Bus

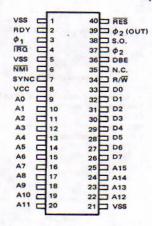

#### R6512 - 40 Pin Package

#### Features of R6512

- 65K Addressable Bytes of Memory (A0-A15)

- IRQ Interrupt

- NMI Interrupt

- RDY Signal

- 8 Bit Bidirectional Data Bus

- SYNC Signal

- Two phase clock input

- Data Bus Enable

| vss 🗖 | 1  | 28 | RES           |

|-------|----|----|---------------|

| φ1 d  | 2  | 27 | $\neg \phi_2$ |

| IRQ - | 3  | 26 | R/W           |

| NMI   | 4  | 25 | D0            |

| VCC = | 5  | 24 | D1            |

| A0 🗆  | 6  | 23 | D2            |

| A1 🗖  | 7  |    | □ D3          |

| A2 🗀  | 8  | 21 | D4            |

| A3 🗖  | 9  | 20 | D5            |

| A4 🗆  | 10 | 19 | D6            |

| A5 _  | 11 | 18 | D7            |

| A6 🗖  | 12 | 17 | A11           |

| A7 🗖  | 13 | 16 | A10           |

| A8 🗖  | 14 | 15 | → A9          |

|       |    |    |               |

#### Features of R6513

- 4K Addressable Bytes of Memory (A0-A11)

- Two phase clock input

- IRQ Interrupt

- NMI Interrupt

- 8 Bit Bidirectional Data Bus

#### R6514 - 28 Pin Package

| vss | 1                     | 28 | RES |

|-----|-----------------------|----|-----|

| φ,  | <b>d</b> <sub>2</sub> | 27 | Φ2  |

| IRO | <b>3</b>              | 26 | R/W |

| VCC | 4                     | 25 | DO  |

| AO  | <b>5</b>              | 24 | D1  |

| A1  | <b>6</b>              | 23 | D2  |

| A2  | <b>4</b> 7            | 22 | D3  |

| A3  | □8                    | 21 | D4  |

| A4  | 9                     | 20 | D5  |

| A5  | 10                    | 19 | D6  |

| A6  | <b>11</b>             | 18 | D7  |

| A7  | 12                    | 17 | A12 |

| A8  | 13                    | 16 | A11 |

| A9  | <b>14</b>             | 15 | A10 |

#### Features of R6514

- 8K Addressable Bytes of Memory (A0-A12)

- Two phase clock input

- IRQ Interrupt

- 8 Bit Bidirectional Data Bus

#### R6515 - 28 Pin Package

#### Features of R6515

- 4K Addressable Bytes of Memory (A0-A11)

- Two phase clock input

IRQ Interrupt

- RDY Signal

- 8 Bit Bidirectional Data Bus

### R6500 NMOS PRODUCTS

#### INSTRUCTION SET

|          | INSTRUCTIONS        | Į. | AME  | DIA | IΕ  | ABS | SOLU | TE  | ZE   | 10 PA | <b>IGE</b> | A   | cue  |      | 186 | PLIE | •   | (M  | 10, 1 | 0   | (10 | 10), 1 | -    | Z. P | AGE. | x    | ABS | X. |     | ABS. | T   | RE  | LATE | VE  | IND | untc | 1 | 21   | AGE. | . 1 | PRO | ES  | -   | *** | 103 |       |     |       |

|----------|---------------------|----|------|-----|-----|-----|------|-----|------|-------|------------|-----|------|------|-----|------|-----|-----|-------|-----|-----|--------|------|------|------|------|-----|----|-----|------|-----|-----|------|-----|-----|------|---|------|------|-----|-----|-----|-----|-----|-----|-------|-----|-------|

| MNEHONIC | OPERATION           | O  | ,    |     |     | OP  | n    |     | OP   |       |            | OP  | n    |      | OP  | 0    |     | OP  |       |     | OP  |        |      | OP   | n    | . 0  | 9 1 |    | 0   | -    |     | OP  |      |     | OP  | 0    |   | OP   | n    |     | 7 ( | 6 : | 5 4 | 3   | 2   | 1 0   | MN  | EMON  |

| ADC      | A+M+C-A (4)(1)      | 65 | 1    | 2   | 2 1 | 50  | 4    | 3   | 65   | 3     |            |     |      |      | 1   |      | _   | _   | _     | 2   | _   | 5      | _    | _    | 4    | 2 71 | -   | -  | -   | 1    | _   |     |      |     | 1   | 1    | 1 | 1    | 1    | 1   |     |     |     |     |     | Z C   |     | A D C |

| AND      | AAM-A (1)           | 25 |      | 2   | 2   | 20  | 4    | 3   | 25   | 3     | 2          |     |      |      |     |      | 1   | 21  | 6     | 2   | 31. | 5      | 2    | 15   | 4    | 2 3  | 0 4 | 13 | 36  |      | 3   |     |      |     |     | -    | 1 | 1    | 1    | 1   | N.  |     |     |     |     | z .   |     | NI    |

| ASL      | C-[2 3]-0           | 1  | 1    |     | 1   | 0E  | 6    | 3   | 06   | 5     | 2          | OA  | 2    | 1    |     | -    | _   | - 1 |       | -   |     |        | -    | 16   | 6    | 2 1  |     |    |     |      |     |     |      |     | - 1 |      | 1 | 1    |      | 1   | N   |     |     |     |     | z c   |     | 151   |

| BCC      | BRANCHONC = 0 (2)   | L  | 1    |     | 1   |     |      |     |      |       |            |     |      |      |     | -    | - 1 | - 1 | - 1   | - 1 | - 1 |        | - 1  | 1    |      | 1    |     | 1  |     |      |     | 90  | 2    | 2   | -   |      | - | 1    |      | ١   |     |     |     |     |     |       | 8   | 3 C C |

| BCS      | BRANCHONC = 1 (2)   |    | 1    |     |     | -   |      |     |      |       | 1          |     |      |      |     | -    |     |     |       | 1   |     |        |      | 1    |      |      |     |    |     |      |     | BO  | 2    | 2   |     |      | 1 |      | 1    | 1   |     |     |     |     |     |       | B   | cs    |

| BEO      | BRANCH ON Z = 1 (2) | Т  | Т    | T   | Т   | ٦   |      |     |      |       |            | П   |      |      | П   |      |     |     | П     | 7   |     |        | 7    | 1    | 1    | 1    | Т   | Т  | т   | T    |     | FO  | 2    | 2   | 1   | 7    | 7 | 1    | 1    | 7   |     |     |     |     |     |       | В   | EQ    |

| BIT      | AAM                 |    | 1    | 1   | 1   | 20  | 4    | 3   | 24   | 3     | 2          | П   |      |      | -1  | - 1  | -   | 1   | - 1   | - 1 | - 1 |        | - 1  | 1    | -    | 1    |     | 1  | 1   | П    |     |     |      |     | 1   |      | 1 |      |      | 1   | w.  |     |     |     |     | z .   |     | 111   |

| 8 M I    | BRANCHONN = 1 (2)   | ı  | ı    | 1   | 1   | 1   |      |     |      |       |            | Н   |      |      | П   | -    | - 1 | - 1 | - 1   | -1  | - 1 |        | - 1  | -1   | -    | 1    | 1   | н  | п   | П    | L   | 30  | 2    | 2   | - 1 | -    | 1 |      | 1    | 1   |     |     |     |     |     |       |     | M     |

| BNE      | BRANCH ON Z = 0 (2) | L  | 1    | 1   | 1   | 1   |      |     |      |       |            | П   |      |      | - 1 |      | 1   | 4   | - 1   | -   | - 1 |        | - 1  | -    | -    | 1    |     | 1  | 1   | 1    |     | 00  |      | 2   | 1   | 1    | 1 | 1    | 1    | 1   |     |     |     |     |     |       | 1   | NE    |

| BPL      | BRANCH ON N = 0 (2) |    |      | 1   | 1   |     |      |     | Н    |       |            |     |      |      |     |      | - 1 |     | - [   | -   |     |        | - 1  |      | П    |      |     |    | 1   |      |     | 10  | 2    | ,   |     |      | - | 1    | -    | 1   |     |     |     |     |     |       | B   | PL    |

| BAK      | BREAK               | T  | T    | T   | 1   | 7   |      |     |      |       |            | П   |      |      | 00  | 7    | 1   | 7   |       | 1   |     | $\neg$ | _    | 7    | +    | +    | +   | +  | +   | +    |     |     | Ť    | Ť   | +   | +    | + | +    | +    | +   |     |     |     | -   | ,   |       |     | RI    |

| BVC      | BRANCH ON V = 0 (2) | 1  | 1    | 1   |     | -   |      |     |      |       |            |     | -    |      |     |      | - 1 |     |       | -   | - 1 |        | - 1  |      |      | 1    |     |    | -   | 1    |     | 50  | 2    | 2   |     |      | 1 |      | 1    | -   |     |     |     |     |     |       |     | ve    |

| BVS      | BRANCHON V = 1 (2)  |    | 1    |     | 1   | -   |      |     |      |       |            | Н   |      |      |     | -    | 1   | -   | - 1   | 1   | - 1 |        | - 1  | 4    | -    | 1    |     |    | L   |      |     |     |      | 2   | -   | -    | - |      | 1    | -1  |     |     |     |     |     |       |     | vs    |

| CLC      | 0-C                 |    | 1    | I   | 1   |     |      | -1  |      |       | 5          |     | -    |      | 18  | 2    |     | 1   | - 1   | - 1 | - 1 | -      | - 1  |      |      | 1    |     | П  | П   |      |     |     |      | 1   | 1   | -    | 1 |      | 1    | 1   |     |     |     |     |     |       | 10  | LC    |

| CLD      | 0-0                 |    | L    | 1   | 1   | 1   |      |     |      |       |            |     |      |      |     | 2    | ,   |     | - 1   | - 1 | _   |        | - 1  |      | -    |      | 1   |    | 1   |      |     |     |      | - 1 |     | -    | 1 | 1    | 1    | 1   |     |     |     | 0   |     |       |     | LO    |

| CLI      | 0-1                 | ۰  | ۰    | t   | +   | +   | -    | -   |      |       |            | Н   | +    | _    | -   | 2    | 1   | +   | +     | +   | -   | -      | +    | +    | +    | +    | +   | ٠  | ٠   | ٠    | -   | Н   | -    | -   | +   | +    | + | +    | +    | +   |     | -   | _   | -   | 0   | _     | -   | _     |

| CLV      | 0-V                 | 1  | 1    | -   | 1   | 1   |      |     |      |       | A          |     |      |      | - 1 | 2    | 1   | -   |       | 1   |     |        | -    | 1    |      |      |     | 1  | 1   | 1    |     |     |      |     | 1   |      | 1 | 1    | 1    | -   |     |     |     |     |     | •     |     | LI    |

| CMP      | A - M               | 1  | 2    |     | 2 0 | ام  | 4    | ,   | CA   | 3     | 2          |     | 1    |      | -   | -    | 1   | C1  | 6     | 2   | Di  | 5      | 2    |      |      | 2 0  | . 4 | ١. | Ox  |      | 1   |     |      | -   | 1   |      | 1 | 1    | 1    | 1   | . ' |     |     |     |     | ::    |     | LV    |

| CPX      | x - M               | EO |      |     | 2 6 |     |      |     |      |       | 2          |     |      |      | 1   |      | 1   | "   | °     | 1   | "   | 1      | 1    | "    | 1    | 10   | 1   | 1, | 10  | 1    | 1 3 |     |      |     |     |      | 1 | 1    |      | 1   |     |     |     | •   |     | z c   | _   |       |

| CPY      | Y-W                 | Ci |      |     | - 1 |     |      | 3   |      | 3     | 2          |     |      |      | -   |      | 1   | 1   |       | 1   |     |        | -    |      |      |      | 1   |    | 1   |      |     |     |      | 1   | 1   |      | 1 | 1    | 1    | 1   |     | ٠.  |     |     |     | ZC    |     | PX    |

| DEC      | M - 1 - M           | ۳  | ۲    | ۲   |     |     | 6    |     |      |       |            | Н   | +    | -    | +   | +    | +   | +   | +     | +   | +   | +      | +    | 1    |      |      | 7   | 1. | +   | +    |     | Н   | -    | +   | +   | +    | + | +    | +    | +   | -   | -   |     | •   | _   | Z C   | _   | PY    |

| DEX      | X-1-X               | 1  | 1    | 1   | ľ   | 1   | 1    | 1   | *    | 3     | "          |     |      |      | A   | ,    | .1  |     | -     | 1   | 1   | -      | 1    | ×    | 6    | 2 0  | 1   | 3  | 1   |      |     |     |      | 1   | 1   |      | 1 | 1    |      | 1   |     | ٠.  |     |     |     | 2 .   |     | EC    |

| DEY      | Y-1-Y               |    | 1    | 1   | 1   | 1   |      | 1   |      |       |            | П   | 1    |      |     | 2    | 1   | -   | П     | 1   | -1  |        | - 1  | 1    |      | 1    | 1   | 1  | 1   |      |     |     | - 1  | П   | -   | 1    | 1 | 1    | -    | 1   | N . |     |     |     |     | 2 .   |     | EX    |

| EOR      |                     |    | ١.   |     | 2 4 |     |      | .1  |      |       |            |     |      | - 1  | 100 | 1    | - 1 |     | . I   | _   |     | . 1    | . 1  |      |      |      |     | ١. | I   |      |     |     |      | - 1 | - 1 | 1    | 1 | 1    | 1    | 1   | N . | ٠.  |     |     |     | z .   | 1 - | EY    |

|          |                     |    | 1    | T   |     |     | - 1  |     |      |       |            |     |      | -    | -   | 1    | ľ   | "   |       | 2   | 51. | 5      |      |      |      | 2 50 |     |    | 59  | 4    | 3   |     | - 1  | - 1 | 1   | 1    | 1 | 1    | -    | 1   | N . |     |     |     |     | z •   | 1   | OR    |

| INC.     | M + 1 -M            | -  | +    | +   | 4   | 4   | 6    | 3   | E6   | 5     | 2          | н   | -    | -    | +   | 4    | 4   | +   | -     | 4   | 4   | 4      | 4    | 8    | 6    | 2 F  | 7   | 3  | 4   | -    |     | Ц   | _    | 4   | -   | 4    | 4 | 4    | 4    | 4   | N · | • • |     | •   | _   | z ·   | _   | N C   |

| INX      | X + 1 - X           |    |      | 1   | 1   | 1   |      | 1   |      |       |            |     |      |      |     | - 1  | 1   | -   |       | 1   | - 1 |        | 1    |      |      |      |     |    | 1   |      |     |     |      | 1   |     |      | 1 | 1    |      | 1   | N . | ٠.  |     |     |     | z •   |     | N X   |

| INY      | Y+1-Y               | ı  | ı    | 1   | 1   | 1   |      |     |      |       |            |     | 1    | 1    | 350 | 2    | 1   | -   | - 1   | - 1 | -1  | - 1    | -1   |      | -    |      | 1   |    | 1   |      |     |     | -    | -   |     | 1    | 1 | 1    | 1    | 1   | N . |     |     |     |     | z •   | 1   | NY    |

| JMP      | JUMP TO NEW LOC     | ı  | 1    | П   |     | C   |      | 3   |      |       |            |     | 1    | -    | 1   | -    | -1  | 1   | - 1   | - 1 | - 1 | -      | - 1  | 1    | -    |      | 1   |    | 1   |      |     |     | - 1  | -   | SC  | 5 :  | 3 | 1    | -    | 1   |     | ٠.  |     |     |     | ٠.    | 1   | M P   |

| JSR      | JUMP SUB            |    | L    | 1   | -   |     | 6    | 3   |      |       |            | -   | 1    | -    | -   | 1    | -   |     | -     | 1   | - 1 |        | - 1  | 1    | 1    |      | 1   | П  | 1   |      |     |     | - 1  | - 1 |     | 1    | ١ | 1    | 1    | 1   |     |     |     |     |     |       |     | SA    |

| LOA      | M - A (1)           |    |      | 1   |     | ND. | 4    | 3   | A5   | 3     | 2          | Н   | +    | -    | +   | 4    | 4   | A1  | 6     | 2 1 | 81  | 5      | 2 1  | 15   | 4    | 8    | 4   | 3  | -   |      | 3   | Н   | _    | 4   | 4   | +    | 4 | 4    | 4    | 4   | N · |     |     | ٠   |     | z •   |     | DA    |

| LDX      | M-X (1)             |    |      |     |     | E   |      | 3   |      |       | 2          |     |      |      |     | 1    |     | 1   | 1     | 1   | -1  |        |      |      |      |      |     |    | 88  | 4    | 3   |     | -    | 1   |     |      | 1 | 36   | 4    | 2   | N · |     |     |     |     | 2 .   |     | D X   |

| LDY      | M-Y (1)             | AO | 2    | 1   |     |     |      |     |      | 3     | 2          |     |      | - 1  | -1  | 1    |     | 1   | -     | 1   | - 1 |        | - 10 |      |      | 2 80 |     |    |     |      |     |     | - 1  | - 1 |     | -    | 1 | 1    | 1    | 1   | N . |     |     |     |     | z •   | L   | DY    |

| LSR      | 0 - F 0- C          | ı  | -    | 1   | 1   | E   | 6    | 3   | 46   | 5     | 2          | 4.4 | 2    | 1    | -   |      | 1   | 1   | -     | 1   | - 1 |        | 1    | 16   | 6    | 2 51 | 7   | 3  |     |      |     |     | -    | -1  |     |      | 1 |      |      | 1   | 0 . |     |     |     |     | z c   | _   | SA    |

| NOP      | NO OPERATION        |    | -    | 1   | 1   |     |      |     |      |       |            |     |      | ľ    | IA. | 2    | 1   | 1   |       | 1   |     |        |      |      | 1    | 1    | 1   |    |     |      |     |     | - 1  | - 1 | 1   | 1    | 1 | 1    |      | 1   |     |     |     |     |     |       | N   | OP    |

| ORA      | AVM-A               | 09 | 12   | ľ   | 2 0 | ю   | 4    | 3   | 05   | 3     | 2          | Ц   | 4    | 4    | 4   | 4    | -   | 11  | 6     | 2   | 11  | 5      | 2    | 5    | 4    | 2 10 | 4   | 3  | 19  | 4    | 3   |     |      | _   | 4   | 4    | 1 |      |      | 4   | N . |     |     |     |     | z •   | 0   | RA    |

| PHA      | A-Ms S-1-5          |    | Г    | T   | Т   | 1   | -    | н   | -    |       | - 1        |     | 1    | - 1  | -   | 3    | 1   | 1   | 1     | 1   | -1  | 1      | 1    | П    | 1    |      | 1   | П  | ı   |      |     |     | - 1  | 1   |     | 1    | 1 | 1    |      | 1   |     |     |     |     |     |       | P   | HA    |

| PHP      | P-Ms S-1-5          |    | ı    | 1   | 1   | 1   | 1    | 1   |      |       | -1         |     | 4    |      |     | 3    | ١.  | 1   | -     | - 1 | - 1 | -      | -    | 1    |      | 1    | 1   |    | 1   | 1    |     |     | 1    | 1   |     | 1    | 1 | 1    | 1    | 1   |     |     |     |     |     | • •   | P   | HP    |

| PLA      | S+1-5 Ms-A          | ı  |      | 1   | 1   | 1   | 1    | 1   |      |       | -          | 1   | 1    |      | -   | 4    | 1   | 1   |       | 1   | - 1 | -      | -    | 1    | 1    | 1    | 1   |    | 1   | 1    |     |     | - 1  | - 1 |     |      | 1 | 1    | i    | 1   | N · | ٠.  |     |     |     | z ·   | P   | LA    |

| PLP      | S+1-S Ms-P          | ı  | ŀ    | 1   | 1   | 1   | 1    | 1   |      |       | 1          | 00  | 1    | - 1  | 26  | 4    | 1   | 1   | 1     | 1   | - 1 | -      | 1    | 1    |      |      | 1   | 1  | 1   |      |     |     | 1    |     | 1   |      | 1 | 1    | 1    | 1   |     | (RI | EST | OR  | EO  |       | P   | LP    |

| ROL      | -[]-[]-             | L  | L    | 1   |     | Ε   |      | 3   |      | 5     |            |     | 2    | 1    | 4   | 4    | 4   | 1   | 4     | 4   | 4   | 4      | _    | -    | 6 3  |      | -   | +- | ┺   |      |     |     |      | _   |     |      | 1 |      |      | 1   | N · |     |     |     |     | Z C   | R   | 01    |

| ROR      |                     |    | 1    | 1   |     | 3   |      | 3   | 66   | 5     | 2          | 64  | 2    | 1    | 1   |      | 1   | -   | 1     | 1   |     |        | 1    | 6    | 6    | 2 78 | 7   | 3  | 1   |      |     |     |      | 1   | T   |      | 1 | 1    | 1    | 1   | N · |     |     |     |     | z c   | A   | OR    |

| RTI      | ATRNINT             |    |      | 1   | 1   | 1   |      | 1   |      | 1     |            |     | 1    |      |     | •    | 1   |     | 1     | 1   |     |        |      | 1    |      |      | 1   | 1  | 1   |      |     |     | 1    | 1   |     |      | 1 | 1    | -    | 1   |     | IRI | EST | OR  | EDI |       | R   | TI    |

| RTS      | RTRN SUB            |    |      |     | 1   | -   |      | 1   |      |       |            |     | 1    | 1    | ю   | 6    | 1   |     | 1     | 1   |     | -      | 1    | 1    | 1    |      | 1   | 1  | 1   |      |     |     | 1    | 1   |     | 1    | 1 | 1    |      | 1   |     |     |     |     |     |       |     | TS    |

| SBC      | A - M - C - A (1)   | E9 | 1 2  | 1   | E   | 0   | 4    | 3   | 65   | 3     | 2          |     | 1    | 1    |     | 1    | 1   | 1   | 6     | 2   | FI  | 5      | 2 1  | 5    | 4    | F    |     | 13 | FS  | 4    | 3   |     | 1    | 1   |     |      | 1 | 1    |      | 1   | N 1 | ٧.  |     |     |     | 2 (3) | 5   | 8 C   |

| SEC      | 1-0                 |    | 1    | 1   | 1   | 1   |      | 1   | 1    | 1     | 1          | 1   |      | - 41 | -   | 2    | 1   | 1   | 1     | 1   |     |        | 1    | 1    | 1    |      | 1   | 1  |     |      |     |     | 1    | 1   | 1   | 1    | - |      | 1    | 1   |     |     |     |     |     | . 1   | 5   | EC    |

| SED      | 1-D                 | L  |      | 1   | 1   |     |      |     |      |       |            |     |      |      |     | 2    | 1   |     |       |     |     |        |      |      |      | 1    |     |    |     |      |     |     |      |     |     |      | 1 |      | 1    |     |     |     |     | 1   |     |       | S   | E 0   |

| SEI      | 1-1                 |    |      | T   | T   | T   |      | T   |      |       |            |     | 1    |      | 8   | 2    | 1   | T   | T     | T   | 1   | T      | T    | T    | T    | T    | Г   |    | Г   |      |     |     |      |     | T   | 1    | 1 | 1    | T    | 1   |     |     |     |     | 1   |       |     | EI    |

| STA      | A-M                 |    |      | 1   |     |     |      |     |      |       | 2          |     | 1    | 1    | 1   | 1    | 1   | 31  | 6     | 2 1 | 91  | 61     | 2 1  | 5    | 4    | 90   | 5   | 3  | 99  | 5    | 3   |     | 1    |     |     |      | 1 | 1    |      | 1   |     |     |     |     |     |       | \$  | T A   |

| STX      | X-M                 |    | -    | 1   |     |     | 4    |     |      |       | 2          |     | 1    | -    | -   | 1    | 1   | 1   | 1     | 1   |     |        | 1    | 1    | -    | 1    | 1   | 1  | 1   |      |     |     | -    | -   | 1   |      | 1 | 100  | 4    | 2   |     |     |     |     |     |       | 5   | TX    |

| STY      | Y-M                 |    |      | 1   | 8   | c   | 4    | 3   | 84   | 3     | 2          |     | 1    |      |     |      | 1   | 1   | 1     | 1   | 1   |        | 1    | 4    |      | 2    | 1   | 1  | 1   |      |     |     | -    | 1   |     | -    | 1 | 1    |      | 1   |     |     |     |     |     |       | 5   | TY    |

| TAX      | A-X                 | L  |      |     |     |     |      |     |      |       |            |     |      | 1    | A   | 2    | 1   |     |       | 1   |     |        |      | 1    |      |      | 1   | 1  |     |      |     |     |      |     |     |      |   | 1    | 1    | 1   |     |     |     |     |     |       |     | AX    |

| TAY      | A-Y                 |    |      | Г   | T   | T   | T    | T   | 1    | 1     | 1          |     | T    | 1    | u   | 2    | 1   | T   | T     | T   | 1   |        | 1    | T    | T    | T    |     | Г  | Г   |      | П   |     | 1    | 1   |     |      | 1 | T    | +    | 1   | N   |     |     |     |     | 2 -   | T   | AY    |

| TSX      | s-x                 | 1  | 1    | 1   | 1   | 1   | 1    | 1   | 1    | 1     | 1          |     | 1    | 1    | IA  | 2    | 1   | 1   | 1     | 1   |     |        |      | 1    | -    | 1    |     |    | 1   |      |     |     |      | 1   |     |      | 1 | 1    |      | 1   | N   |     |     |     |     |       | T   | SX    |

| TXA      | X-A                 |    | 1    |     | 1   |     | 1    | 1   | 1    | 1     | 1          |     | 1    | 1    | A   | 2    | ,   | 1   | 1     | 1   | 1   |        | -    | 1    | 1    | 1    | 1   |    |     |      |     |     | -    | 1   |     | 1    | 1 | 1    |      | 1   | N . |     |     |     |     |       |     | XA    |

| TXS      | x-s                 |    | 1    | 1   |     | 1   | 1    | 1   |      |       |            |     | 1    |      |     | 2    | 1   | 1   | 1     | 1   | 1   |        |      |      |      | 1    | 1   |    | 1   |      |     |     |      | 1   |     | 1    | 1 | -    | -    | -   |     |     |     |     |     |       |     | x s   |

| TYA      | Y-A                 |    | L    | 1   | 1   |     |      |     |      |       |            |     | 1    | 1    |     | 2    | 1   | 1   | 1     | 1   | 1   | 1      | 1    | 1    |      |      | 1   | 1  | 1   |      |     |     |      | 1   |     |      | 1 | 1    | 1    | 1   | N . |     |     |     |     | 2 -   |     | YA    |

|          | (1) ADD 110         | N  | IF F | PAG | € 8 | ou  | NOA  | RY  | 150  | RO    | SSE        | 0   | -    |      | -   | -    | _   | -   | -     | 1   | -   | ×      | -    | IN.  | XEX  | -    | -   | -  | -   |      |     | _   | -    | -   |     | -    | - | -    | +    | -   | _   | -   | 4.  | -   | -   |       | _   |       |

|          | (2) ADD 1 TO        | -N | IF   | BR  | ANC | H   | occ  | uge | 5.70 |       | ME         | PAG | E    |      |     |      |     |     |       | 1   |     | 2      |      |      | XEX. |      |     |    |     |      |     |     |      |     |     | AC   |   | RAC  |      |     |     |     |     |     |     | HYR   |     |       |

|          | ADD 2 TO            |    |      |     |     |     | occ  | UAS | STC  | DIE   | FE         | REN | T PA | AGE  |     |      |     |     |       | 1   |     |        |      |      |      | ULA  | TOR |    |     |      |     |     |      |     | ٨   | AN   |   |      |      |     |     | 0   |     |     |     | YCL   |     |       |

|          | (4) IF IN DECI      |    |      |     |     |     | 40   |     | wee  | 110   |            |     |      |      |     |      |     |     |       | 1   |     | M      | 4    |      |      |      |     |    | CTI | E A  | DDA | ESS |      |     | v   | OF   |   |      |      |     |     |     |     |     |     | YTES  |     |       |

|          | ACCUMUL             | AT | OR   | MU  | ST  | BE  | CHE  | CK  | EDF  | OR    | ZEF        | ROR | ESU  | LT   |     |      |     |     |       | 1   |     | N      | 41   |      |      |      |     |    |     | DINT |     |     |      |     | v   |      |   | USIN | EO   | A   |     | -   |     | -   | -   | 11/1  |     |       |

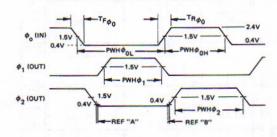

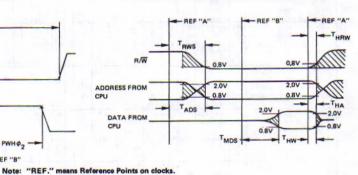

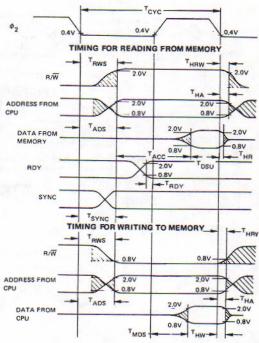

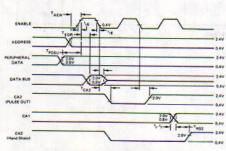

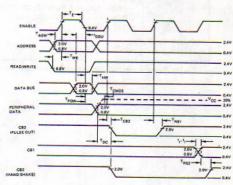

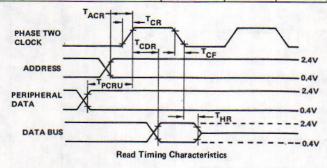

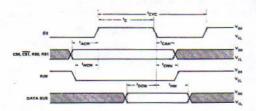

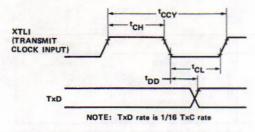

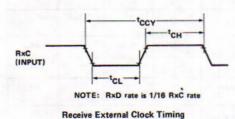

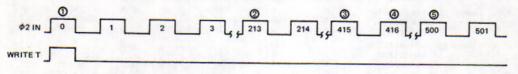

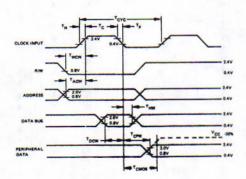

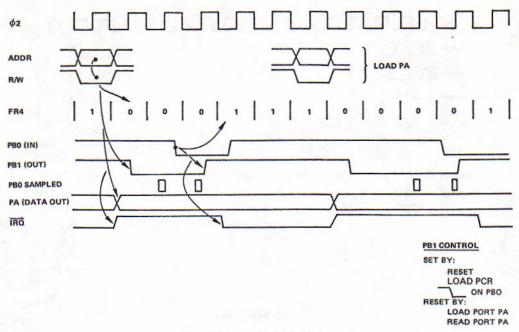

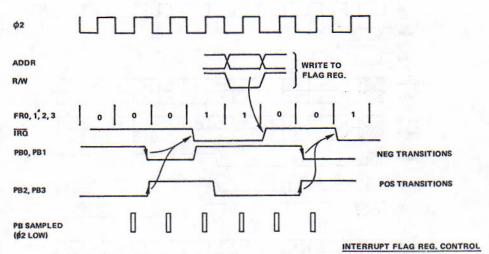

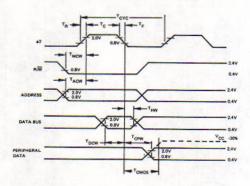

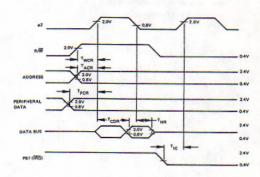

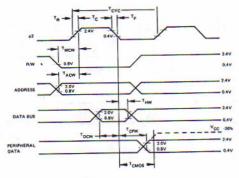

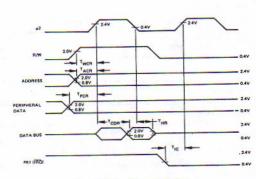

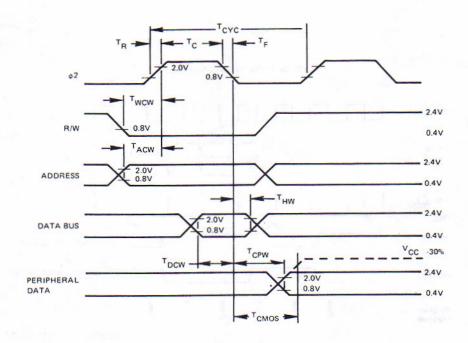

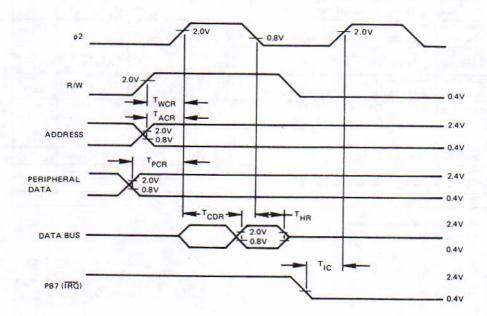

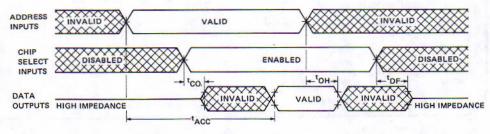

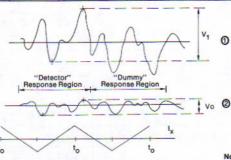

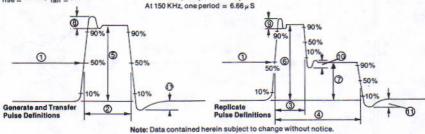

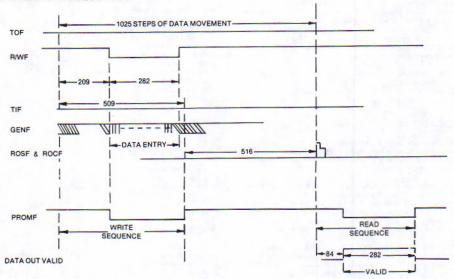

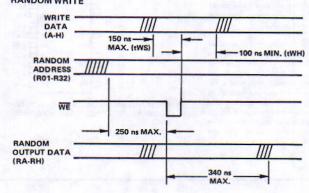

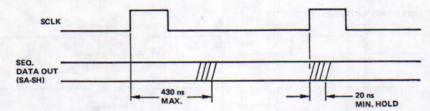

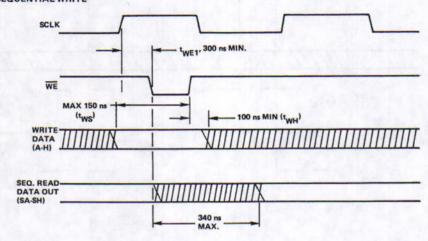

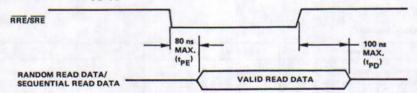

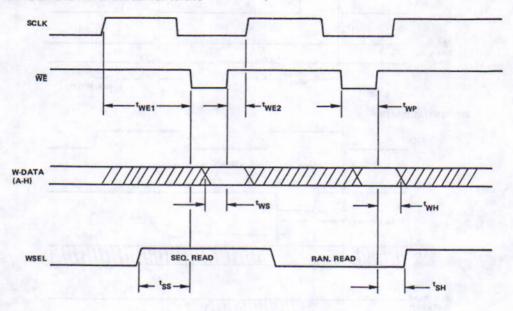

#### Timing for Reading Data from Memory or Peripherals

Clock Timing - R6512, 13, 14, 15

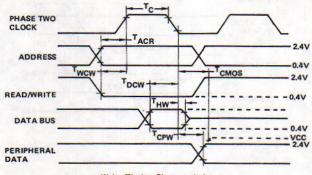

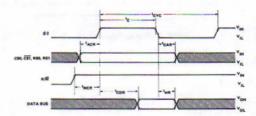

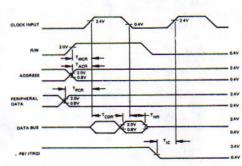

#### Timing for Writing Data to Memory or Peripherals

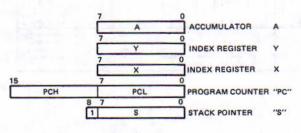

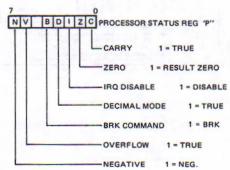

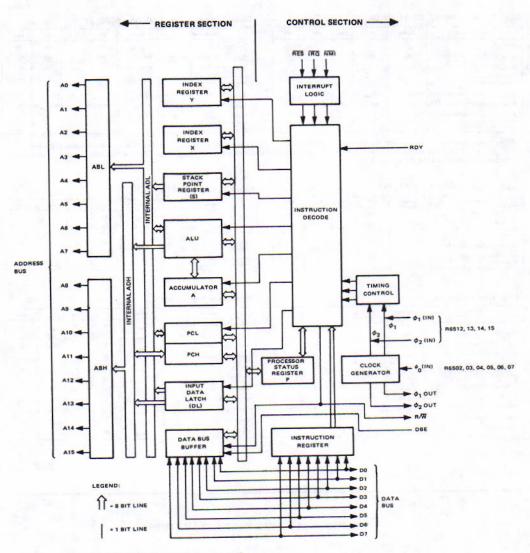

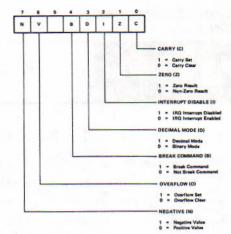

#### PROGRAMMING MODEL

### R6500 NMOS PRODUCTS

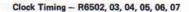

#### Clock Timing - R6502, 03, 04, 05, 06, 07

| Characteristic                                                                                                                                   | Symbol            | Min        | Тур | Mex        | Unit |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|------------|-----|------------|------|

| Cycle Time                                                                                                                                       | Toyo              | 1,0        | -   | 10.0       | þs   |